# The Axion-CL

# **Hardware Reference Manual**

BitFlow, Inc. 400 West Cummings Park, Suite 5050 Woburn, MA 01801 USA

Tel: 781-932-2900

Sales: sales@bitflow.com

Support: support@bitflow.com

Web: www.bitflow.com

Revision A.3

# © 2024 BitFlow, Inc. All Rights Reserved.

This document, in whole or in part, may not be copied, photocopied, reproduced, translated or reduced to any other electronic medium or machine readable form without the prior written consent of BitFlow, Inc.

BitFlow, Inc. makes no implicit warranty for the use of its products and assumes no responsibility for any errors that may appear in this document, nor does it make a commitment to update the information contained in.

BitFlow, Inc. retains the right to make changes to these specifications at any time without notice.

All trademarks are properties of their respective holders.

#### Revision History:

| Revision | Date       | Comments                                       |

|----------|------------|------------------------------------------------|

| A.0      | 2016-04-05 | First printing                                 |

| A.1      | 2017-12-16 | Updates, synchronized to SDK 6.30              |

| A.2      | 2021-03-03 | Added 1xB, 2xB, 4xB and synchronize to SDK 6.5 |

| A.3      | 2024-04-15 | Synchronize to SDK 6.6                         |

# **Table of Contents**

#### P - Preface

Purpose AXN-P-1

Support Services AXN-P-1 Technical Support AXN-P-1 Sales Support AXN-P-1

Conventions AXN-P-2

Bitfield definitions AXN-P-3

Example Bitfield Definition AXN-P-3 Bitfield Definition Explanation. AXN-P-3

#### 1 - General Description and Architecture

The Axion-CL family AXN-1-1

Camera Link AXN-1-1

Virtual vs. Hardware AXN-1-1

The Virtual Frame Grabber (VFG) AXN-1-2

Axion Configuration Spaces AXN-1-2

General Description AXN-1-3

Video Data AXN-1-7

Camera Control AXN-1-7

Camera Link Trigger Support AXN-1-8

Axion I/O system AXN-1-8

The Timing Sequencer Signal Generator AXN-1-8

The StreamSync System AXN-1-8

The Volume Of Interest Acquisition Engine AXN-1-9

Camera Link Camera Power (PoCL) AXN-1-9

Firmware AXN-1-10

Axion Camera Configuration Files AXN-1-11

BFML Camera File Modes AXN-1-11

The Axion Models AXN-1-12

## 2 - The StreamSync Acquisition Engine

Introduction AXN-2-1

The StreamSync Acquisition Engine World AXN-2-2

Controlling the StreamSync Acquisition Engine AXN-2-2

Observing the StreamSync Acquisition Engine AXN-2-4

Synchronizing the StreamSync Acquisition Engine With a CXP Camera AXN-2-4 Synchronizing the StreamSync Acquisition Engine With a Camera Link Camera

Regions Of Interest (ROI) with the StreamSync Acquisition Engine. AXN-2-5

Window Interrupts AXN-2-7

AE State Machine AXN-2-8

Triggering the StreamSync Acquisition Engine AXN-2-9

Comparing the StreamSync Acquisition Engine to Other BitFlow products AXN-2-10

AE\_CON AXN-2-11

AE\_STATUS AXN-2-13

AE STREAM SEL AXN-2-15

V\_WIN\_DIM AXN-2-17

Z\_WIN\_CON AXN-2-19

Z WIN DIM AXN-2-23

Z\_WIN\_DIM\_EXT AXN-2-25

Y\_INT\_DEC AXN-2-27

Y WIN CON AXN-2-29

Y\_WIN\_DIM AXN-2-33

Y\_WIN\_DIM\_EXT AXN-2-35

X\_WIN\_DIM AXN-2-37

X\_WIN\_DIM\_EXT AXN-2-39

V ACQUIRED AXN-2-41

Z ACQUIRED AXN-2-43

Y\_ACQUIRED AXN-2-45

X ACQUIRED AXN-2-47

CON489 AXN-2-49

CON490 AXN-2-52

CON548 AXN-2-54

CON549 AXN-2-57

SF\_DIM AXN-2-60

SF\_CON AXN-2-62

IMAGE\_STAMP\_CTRL AXN-2-65

## 3 - The StreamSync Buffer Manager

Introduction AXN-3-1

The Buffer Manager Details AXN-3-2

CON485 Register AXN-3-3

CON486 Register AXN-3-5

BUF\_MGR\_CON AXN-3-7

BUF\_MGR\_TIMEOUT AXN-3-9

**BOARD CONFIG AXN-3-11**

PACKETS\_SENT\_STATUS AXN-3-13

QUADS\_USED\_STATUS AXN-3-15

QTABS USED STATUS AXN-3-17

PKT\_STAT AXN-3-19

QUADS\_LOADED\_STATUS AXN-3-22

QTABS LOADED STATUS AXN-3-24

BUF\_MGR\_STATUS AXN-3-26

PKT\_CON AXN-3-29

#### 4 - Timing Sequencer

Introduction AXN-4-1

The Auxiliary Timing Sequencer AXN-4-1

Description AXN-4-1

TS\_CONTROL AXN-4-4

TS\_TABLE\_CONTROL AXN-4-9

TS\_TABLE\_ENTRY AXN-4-11

ATS\_CONTROL AXN-4-15

ATS\_TABLE\_CONTROL AXN-4-19

ATS\_TABLE\_ENTRY AXN-4-21

#### 5 - The Aon, Axion, Claxon and Cyton I/O System

Introduction AXN-5-1

Concepts AXN-5-1

I/O Between Virtual Frame Grabbers AXN-5-1

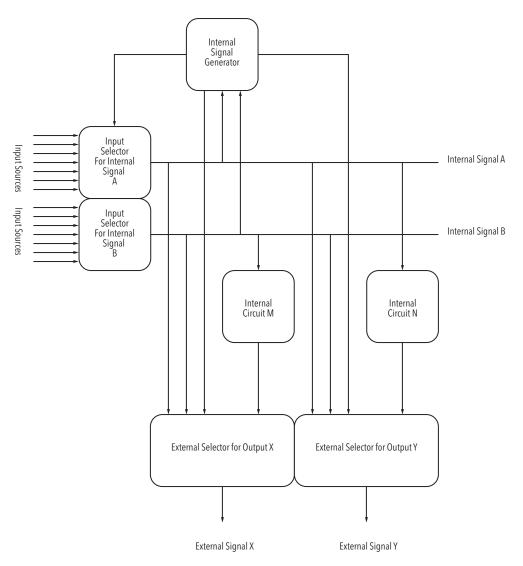

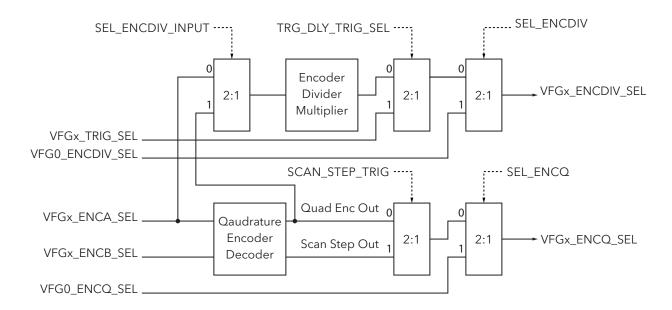

Overview of the I/O System Routing AXN-5-3

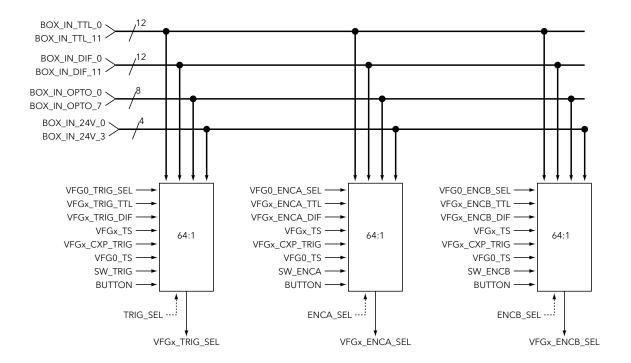

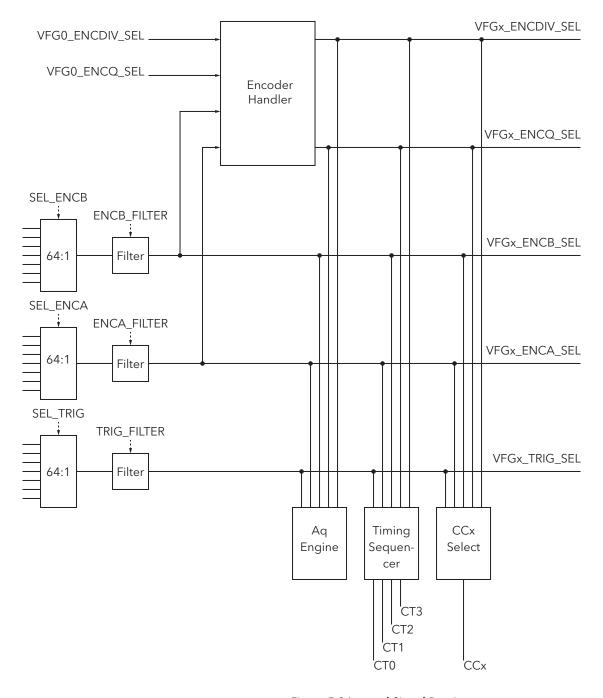

Input Selection AXN-5-4

Internal Signals AXN-5-5

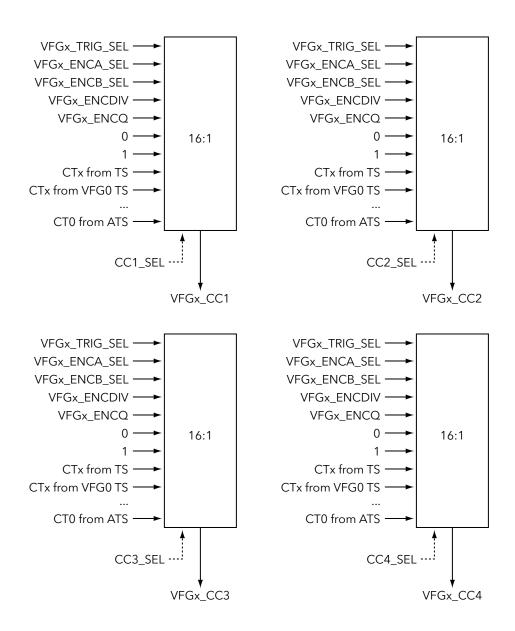

Output Signal Selection AXN-5-8

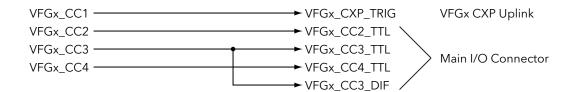

I/O Connector Output Signal Routing AXN-5-9

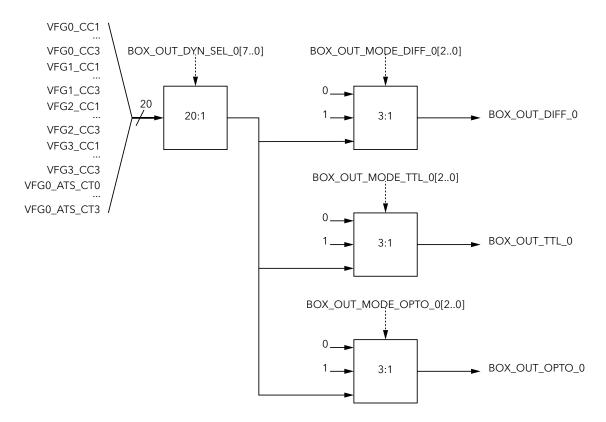

BitBox Output Signal Routing AXN-5-10

### 6 - The I/O System Registers

Introduction AXN-6-1

CON60 AXN-6-2

CON61 AXN-6-4

CON62 AXN-6-6

CON63 AXN-6-10

CON64 AXN-6-16

TRIG\_OPTS AXN-6-21

ENCA\_OPTS AXN-6-23

ENCB\_OPTS AXN-6-25

BOX\_OUT\_DYN\_SEL\_SET\_A AXN-6-27

BOX\_OUT\_DYN\_SEL\_SET\_B AXN-6-30

BOX\_OUT\_DYN\_SEL\_SET\_C AXN-6-32

BOX\_OUT\_MODE\_SET\_A AXN-6-34

BOX\_OUT\_MODE\_SET\_B AXN-6-39

BOX\_OUT\_MODE\_SET\_C AXN-6-44

#### 7 - Encoder Divider

Introduction AXN-7-1

Encoder Divider Details AXN-7-2

Formula AXN-7-2

Example AXN-7-2

Restrictions AXN-7-2

PLL Locking AXN-7-3

Handling Encoder Slow Down or Stopping AXN-7-3 Encoder Divider Control Registers AXN-7-4

#### 8 - Quadrature Encoder

Introduction AXN-8-1

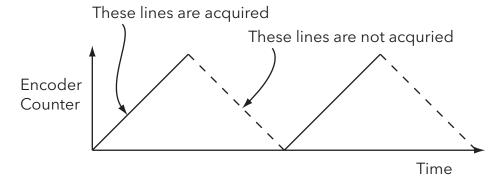

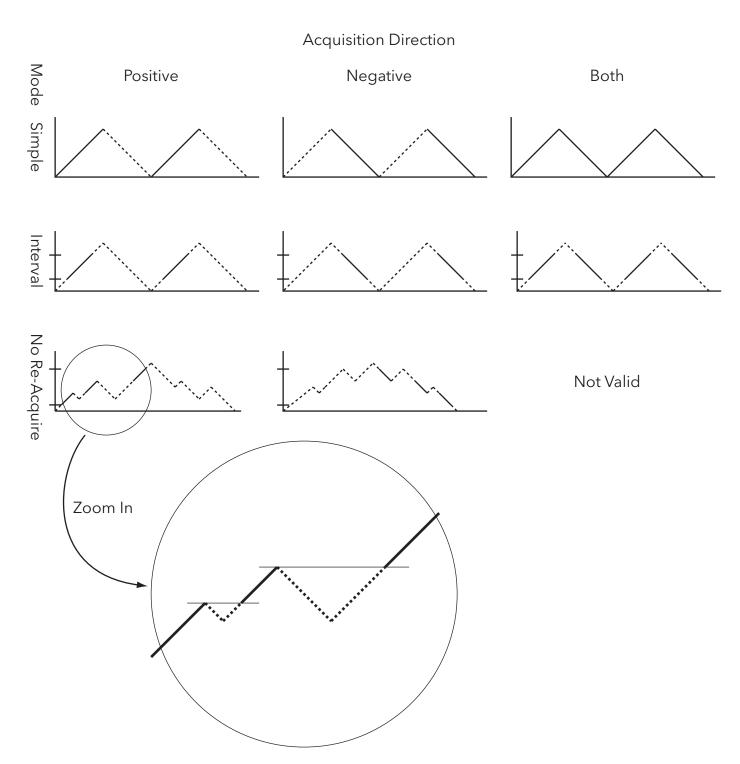

Simple Encoder Mode AXN-8-1

Positive or Negative Only Acquisition AXN-8-1

Interval Mode AXN-8-2

Re-Acquisition Prevention AXN-8-2

Scan Step Mode AXN-8-2

Combining Modes AXN-8-2

Control Registers AXN-8-2

Observability AXN-8-3

**Electrical Connections AXN-8-3**

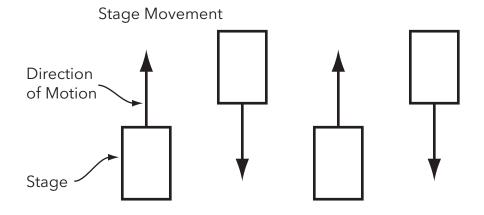

Understanding Stage Movement vs. Quadrature Encoder Modes AXN-8-4

#### 9 - Quadrature Encoder and Divider Registers

Introduction AXN-9-1

CON65 Register AXN-9-2

CON66 Register AXN-9-4

CON67 Register AXN-9-7

CON68 Register AXN-9-10

CON69 Register AXN-9-12

#### **10 - System Probe**

Introduction AXN-10-1

System Probe Constants AXN-10-2

List of System Probe Events AXN-10-2

List of System Probe Functions AXN-10-3

List of System Probe Counting Modes AXN-10-4

System Probe Examples AXN-10-5

Example - Clocks per Line AXN-10-5

Example - Camera Frame Rate AXN-10-5

SP\_EVENTS AXN-10-7

SP CON AXN-10-10

SP\_STAT AXN-10-13

SP LIMIT AXN-10-15

#### 11 - Axion Camera Link Registers

Introduction AXN-11-1 CL\_IOBUF\_CTL AXN-11-2 CL\_CHAN\_CONFIG AXN-11-4

UART CON BASE AXN-11-7 UART RDAT BASE AXN-11-10 CL\_CON\_BASE AXN-11-12 TAP CON BASE AXN-11-14 TAP TABLE ADDR BASE AXN-11-16 TAP\_TABLE\_DAT\_BASE AXN-11-18 FLASH\_CON\_BASE AXN-11-20 FLASH ADDR BASE AXN-11-23 FLASH\_DAT\_BASE AXN-11-25 TAP DIPR CONTROL AXN-11-27 CLMON\_FVAL\_EXP AXN-11-29 CLMON\_LVAL\_EXP AXN-11-31 CLMON FVAL COUNT AXN-11-34 CLMON LVAL B COUNT AXN-11-36 CLMON\_LVAL\_M\_COUNT AXN-11-38 CLMON LVAL F COUNT AXN-11-40

#### 12 - Axion Power and Miscellaneous Registers

Introduction AXN-12-1 CON104 AXN-12-2

CON105 AXN-12-5

CON106 AXN-12-7

CON136 AXN-12-9

CON137 AXN-12-12

CON138 AXN-12-14

CON168 AXN-12-16

CON169 AXN-12-19

CON170 AXN-12-21

CON200 AXN-12-23

CON201 AXN-12-26

CON202 AXN-12-28

CON356 AXN-12-30

CON357 AXN-12-32

#### 13 - Specifications

Introduction AXN-13-1 PCI Express Compatibility AXN-13-3 Maximum Pixels Per Line AXN-13-4 Maximum Lines Per Frame AXN-13-5 Axion Power Requirements AXN-13-6

#### 14 - Mechanical

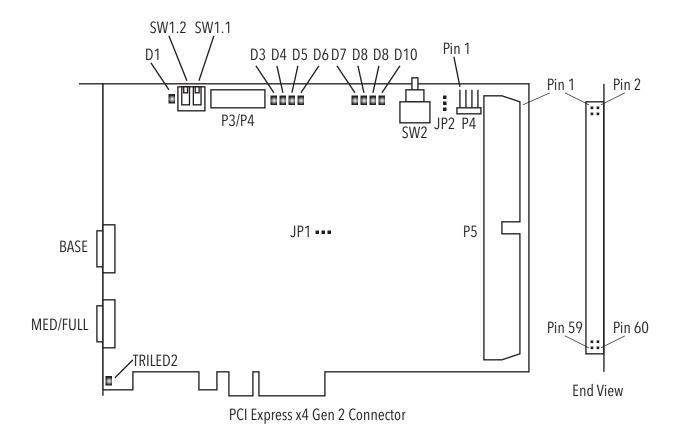

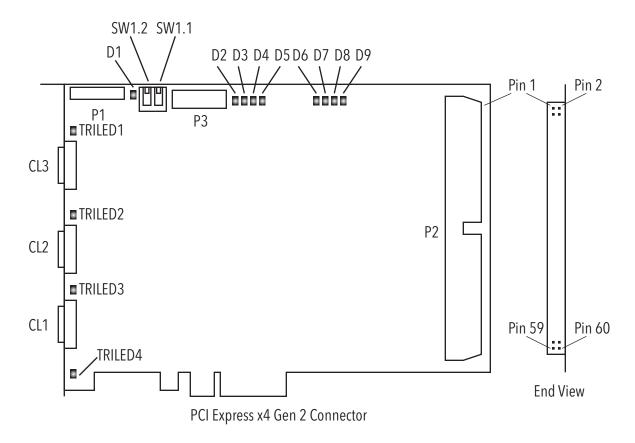

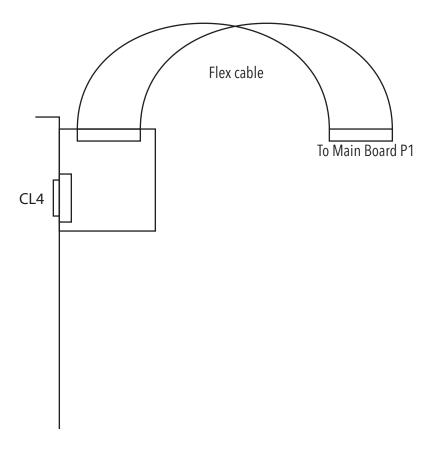

Introduction AXN-14-1

The Axion-CL Connectors AXN-14-9

The CL Connectors AXN-14-9

Switches AXN-14-11

Jumpers AXN-14-12

Jumper JP1 AXN-14-12

Jumper JP2 AXN-14-12

LEDs AXN-14-13

Camera Status LEDS AXN-14-14

Button AXN-14-15

The Auxiliary Power Connector AXN-14-16

The BitBox Box Connector AXN-14-17

I/O Connector Pinout for the Axion-1xE, Axion-2xE and Axion-4xB AXN-14-18

I/O Connector Pinout for the Axion-1xB AXN-14-20

I/O Connector Pinout for the Axion-2xB AXN-14-21

Preface Purpose

# **Preface**

# Chapter P

## P.1 Purpose

This Hardware Reference Manual is intended for anyone using an Axion-CL frame grabber. The purpose of this manual is two-fold. First, this manual completely describes how the board works. Second, it is a reference manual describing in detail the functionality of all of the board's registers.

#### P.1.1 Support Services

BitFlow, Inc. provides both sales and technical support for the Axion family of products.

#### P.1.2 Technical Support

Our web site is www.bitflow.com.

Technical support is available at 781-932-2900 from 9:00 AM to 6:00 PM Eastern Standard Time, Monday through Friday.

For technical support by email (support@bitflow.com) or by FAX (781-933-9965), please include the following:

Product name

Camera type and mode being used

Software revision number

Computer CPU type, PCI chipset, bus speed

Operating system

Example code (if applicable)

## P.1.3 Sales Support

Contact your local BitFlow Sales Representative, Dealer, or Distributor for information about how BitFlow can help you solve your most demanding camera interfacing problems. Refer to the BitFlow, Inc. web site (www.bitflow.com) for a list of North American representatives and worldwide distributors.

Purpose The Axion-CL

## P.1.4 Conventions

Table P-1 shows the conventions that are used for numerical notation in this manual.

Table P-1 Base Abbreviations

| Base        | Designator | Example |

|-------------|------------|---------|

| Binary      | b          | 1010b   |

| Decimal     | None       | 4223    |

| Hexidecimal | h          | 12fah   |

Table P-2 shows the numerical abbreviations that are used in this manual.

Table P-2 Numeric Abbreviations

| Abbreviation | Value   | Example |  |

|--------------|---------|---------|--|

| К            | 1024    | 256K    |  |

| М            | 1048576 | 1 M     |  |

Preface Bitfield definitions

# P.2 Bitfield definitions

# P.2.1 Example Bitfield Definition

is what each bitfield definition looks like:

**BITFIELD** R/W, CON0[7..0], Axion-CL

Bitfield discussion.

# P.2.2 Bitfield Definition Explanation.

The definitions is broken into three sections (see Table P-3).

Table P-3 Bitfield Sections.

| Section             | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bitfield name       | This is the name of the bitfield. This name is use to program this bitfield from software or from within and camera configuration file. When programming bitfields from software using a Peek or Poke function, the bitfield is preceded with "REG_". For example the bitfield CFREQ is referred to in software as REG_CFREQ.                                                                                                                                                                                                                                                                                        |

| Bitfield details    | This section describes how the bitfield is accessed. The first part describes the how the bits can be accessed. For example R/W means the register can be both read and writen. See the Table P-4 for details. The second part is the wide register that the bitfield is located in. In the example above this bitfield is in CONO. Following the wide register name is a bitfield location description, in hardware engineering format. For example, [70], means the bitfield has 8 bits, location in positions 0 to 7. Finally this section also indicates if the register is specific to only one product family. |

| Bitfield discussion | This section explains the purposed of the bitfield in detail.<br>Usually meaning of every possible value of the bitfield is<br>listed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Bitfield definitions

The Axion-CL

Table P-4 explains the abbreviations used in the bitfield definitions.

Table P-4 Abbreviations

| Access     | Meaning                                                                             |

|------------|-------------------------------------------------------------------------------------|

| R/W        | Bitfield can be read and written.                                                   |

| RO         | Bitfield can only be read. Writing to this bit has no effect.                       |

| WO         | Bitfield can only be written. Reading from this bit will return meaningless values. |

| Karbon-CL  | This bitfield is functional only the Karbon-CL.                                     |

| Karbon-CXP | This bitfield is functional only the Karbon-CXP.                                    |

| Neon       | This bitfield is functional only the Neon                                           |

| R64        | This bitfield is functional only the R64 family.                                    |

| Alta       | This bitfield is functional only the Alta family.                                   |

| Cyton-CXP  | This bitfield is functional only on the Cyton-CXP family                            |

| Axion-CL   | This bitfield is functional only on the Axion-CL family                             |

| Aon-CXP    | This bitfield is functional on the Aon-CXP family                                   |

| Claxon-CXP | This bitfield is functional on the Axion-CXP family                                 |

AXN-P-4 BitFlow, Inc. Version A.3

# General Description and Architecture

# Chapter 1

# 1.1 The Axion-CL family

The purpose of this chapter is to explain, at a block diagram level, how the Axion-CL works. Currently there are five main models in the Axion-CL family:

AXN-PC2-1xE, support for one Base, Medium, Full or 80-bit camera

AXN-PC2-2xE, support for two Base, Medium, Full or 80-bit cameras

AXN-PC2-1xB, supports for one Base camera

AXN-PC2-2xB, supports for two Base cameras

AXN-PC2-4xB, supports for four Base cameras

#### 1.1.1 Camera Link

In order to understand how the Axion-CL works, it is helpful to understand the basics of Camera Link. It is beyond the scope of this manual to describe how Camera Link works, however, more information on the Camera Link specification is available from http://www.visiononline.org/.

#### 1.1.2 Virtual vs. Hardware

It's important to understand how this manual works. Some chapters of this manual discuss the Axion-CL as a hardware platform (this chapter is a good example). While other chapters discuss the details of the virtual frame grabbers (VFG) that this hardware platform supports. The concept of the virtual frame grabber is described below, but basically the idea is that one hardware platform can support more than one device. In the case of the Axion-CL, these devices are frame grabbers.

Note that we are not using the word virtual in the sense of "a software virtualization of a hardware device", these VFGs are real hardware. The reason we using "virtual" is because the term "frame grabber" has more than one meaning. It can mean the piece of hardware that you put in your computer, or it can mean the device that the your software application is controlling and getting images from. For the purposes of this manual, "virtual frame grabber" means the device that your application is interfaces with. While this might sound complicated, the implementation is simple. You plug our Axion-CL frame grabber into your PC, and your application interacts with one or more VFGs available. Everything else is taken care of by the BitFlow drivers.

The Axion-CL family The Axion-CL

#### 1.1.3 The Virtual Frame Grabber (VFG)

The idea behind the VFG is to separate the hardware platform (connectors, laminate, FPGAs, etc.) from the frame grabbing functionality that software applications work with. The primary reason behind this separation is that the turn around time for hardware is much longer than the turn around time for modifying virtual frame grabbers. To create a brand new virtual frame grabber, or to modify an existing one, simply requires writing new firmware or updating existing firmware.

The idea of modifying a frame grabber by making changes to its firmware is not new. BitFlow has been doing this since its very first product. However, unique to BitFlow products is the fact the entire frame grabber is written in firmware. The only fixed hardware components are the interfaces to the outside world (e.g. the interface chips on the front end). Everything else that makes up the board, camera control, data buffering, DMA engine, etc. is written in firmware. This gives the platform incredible levels of flexibility and opens the door to unlimited customization.

#### 1.1.4 Axion Configuration Spaces

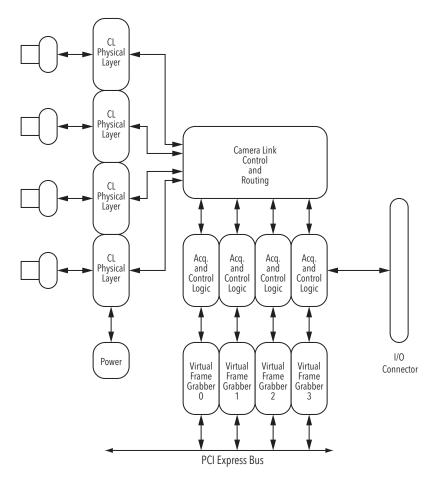

The Axion-CL model supports up to four VFGs. Each VFG appears to operating system and your software as a separate device. The block diagrams for the different models are shown in the following section.

AXN-1-2 BitFlow, Inc. Version A.3

# 1.2 General Description

The Axion-CL is a x4 PCI Express Gen 2 board. It can work in any PCI Express slot that it can fit it. Usually this means an x4, x8 or x16 slot. However, some mother boards have x1 slots with x4 connectors. The Axion-CL will work in these slots, although performance my be somewhat reduced. The Axion-CL is a Gen 2 PCIe device, but it will work in Gen 1 slots, though DMA performance will be degraded. DMA performance will be the same for both Gen 2 and Gen 3 slots.

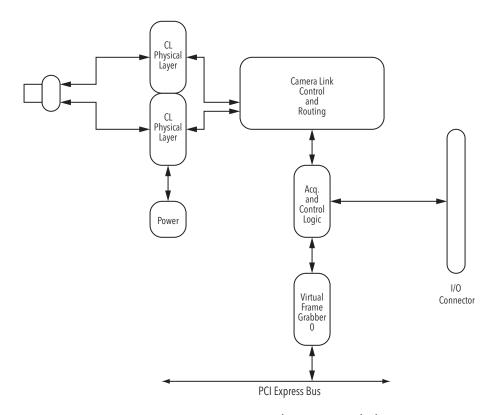

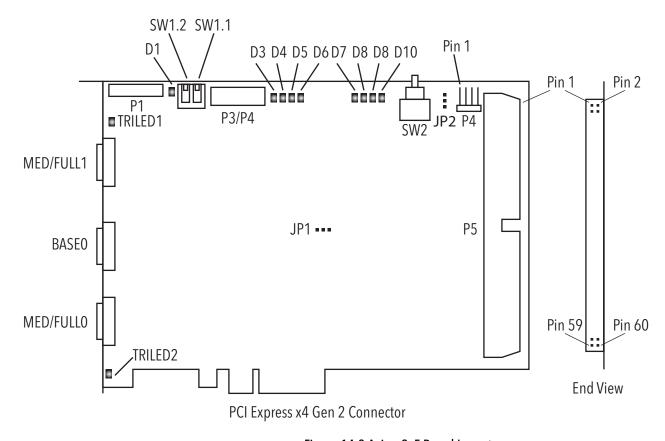

Figure 1-1 The Axion-1xE Block Diagram

General Description The Axion-CL

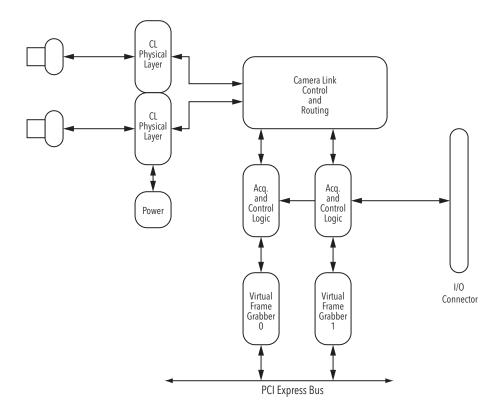

Figure 1-2 The Axion-2xE Block Diagram

AXN-1-4 BitFlow, Inc. Version A.3

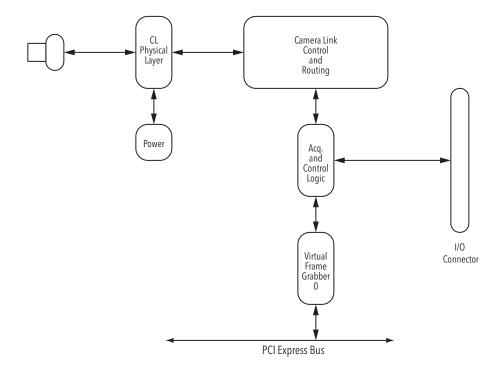

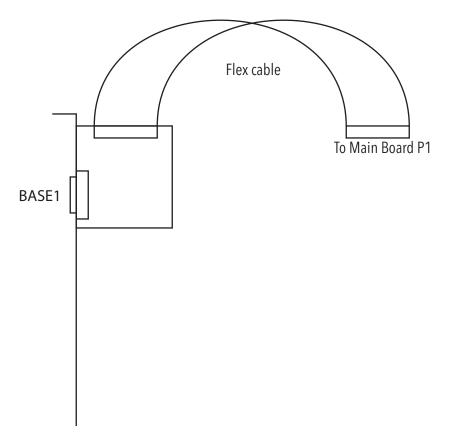

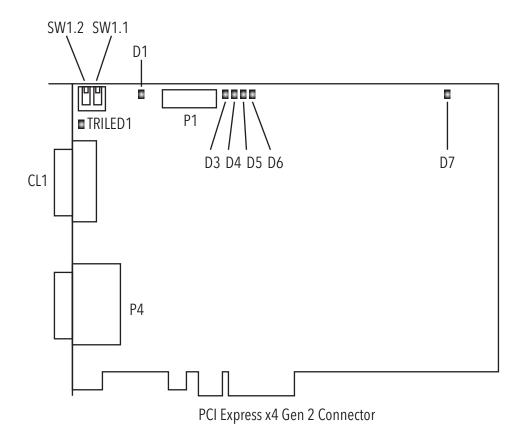

Figure 1-3 The Axion-1xB Block Diagram

General Description The Axion-CL

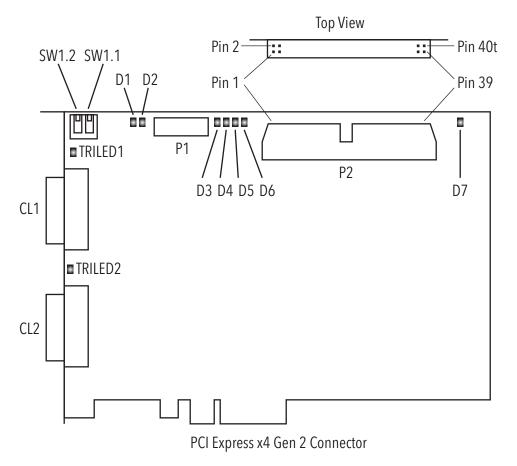

Figure 1-4 The Axion-2xB Block Diagram

AXN-1-6 BitFlow, Inc. Version A.3

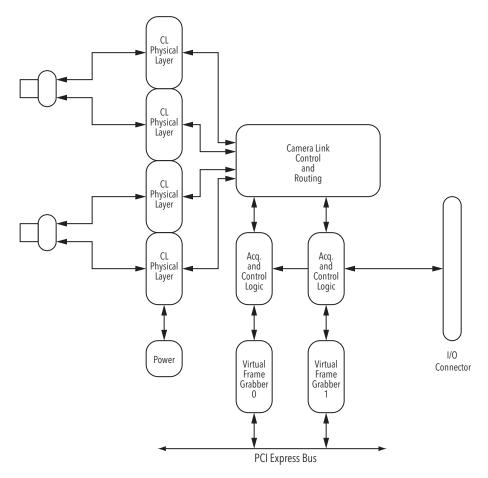

Figure 1-5 The Axion-4xB Block Diagram

#### 1.2.1 Video Data

Camera Link Video data is parallel digital data. The Camera Link physical layer takes a number of parallel signals and "serializes" them on to a small number of high speed signals. One the frame grabber size, the data is "de-serialized". The video data is not sent it packets. Synchronization is achieved via individual clock and synchronization signals. Data width can be from 8 to 80 bits.

#### 1.2.2 Camera Control

Camera Link facilities camera control via a RS232 serial connection. The Camera Link cable contains a bidirectional serial link. This can be used to send and receive control data to/from the camera. The serial link is always synchronous. The camera does not send data without being requested from the host.

General Description The Axion-CL

The Camera Link specification requires frame grabber manufactures to provide a serial communications DLL which exposes a communications API. This API is open and can be used by customers in their own software. This is installed automatically when the BitFlow SDK installer is run.

Each camera vendor has its on Camera Link control protocol. There is no standard. Most camera vendors provide a Camera Control utility which uses the frame grabber serial DLL to communicate through the frame grabber to the camera. Most camera vendors also document their protocol so end users can directly program their cameras.

#### 1.2.3 Camera Link Trigger Support

Camera Link supports very low latency triggering (from the frame grabber to the camera) via four dedicated signals CC1, CC2, CC3 and CC4. These can be driven by a number of different sources on the Axion-CL.

#### 1.2.4 Axion I/O system

The Axion-CL has a sophisticated I/O system, which is extremely flexible. The system take in many inputs, routes them to a number of internal signals which can be further manipulate, then routes the results to a wide rand of outputs. The I/O system is discuss in more detail in Section 7.1.

#### 1.2.5 The Timing Sequencer Signal Generator

With the introduction of the Axion-CL BitFlow introduced a new signal generator, the Timing Sequencer. The Axion-CL also uses this timing generator. The Timing Sequencer (TS) is more flexible and more power than the timing generators used on early BitFlow frame grabbers. It has the ability to output multiple different size pulses, each of which can free-run or require a trigger. The TS is more accurate than the NTG and has a finer granularity. The TS can also be changed on the fly, with switch overs to the new timing exactly synchronized. See section 4.1 for more information.

## 1.2.6 The StreamSync System

Starting with the Cyton-CXP, BitFlow introduced a new DMA engine, the Axion-CL has this same engine. It is designed from scratch acquisition and called the StreamSync system. The StreamSync system has been designed to optimize acquisition and DMA throughput over the PCIe bus given a wider variety of internal PC conditions. In addition, the Stream Sync system has been designed to automatically resync and recover should t every be packet lost (either on the input or the output side of the board), resulting in much more usable and fault tolerant image sequences in host memory. For more information see Section 2.1 and Section 3.1.

#### 1.2.7 The Volume Of Interest Acquisition Engine

The Axion-CL introduces the concept of Volume of Interest (VOI) as part of its Stream-Sync Acquisition Engine. This has been designed from the ground up to satisfy the needs of real world machine vision application. The VOI provide robust and flexible programming that can handle of a wide variety of pixel, line, frame and sequence acquisition commands either manually from software control, or externally via hardware triggers. There is full support for X and Y offsets, X and Y Region of interests, sequences and sequences of sequences. See section 2.2 for more information.

#### 1.2.8 Camera Link Camera Power (PoCL)

The Camera Link PoCL specification specifies that the frame grabber provide up to 4W at 12V for powering an attached camera. The Axion-CL conforms to this specification and provides power on all of its CL connectors. This can provide up to 8 W for medium/full/80-bit Camera Link cameras. Some cameras do not require power, so the Axion-CL can optionally turn power on or off via its registers. Normally this information is part of the camera configuration file, thus files for cameras that require power are so indicated.

The Axion-CL automatically powers up all connectors that need power (i.e. correctly respond to the sense circuit). This happens as soon as the system is booted.

The Axion-CL constantly monitors the current on each Camera Link connector, if either over current or under current conditions exist, the power will be turned off. The monitoring system is purely in hardware, so no host computer intervention is required in order to safeguard the power source.

For situation where the camera requires more power than the PCIe bus can supply to the frame grabber, the P4 connector can be use. This connector can connect to the PC's power supply and all camera power will come from this connector.

Firmware The Axion-CL

#### 1.3 Firmware

Unlike many of BitFlow's previous models of frame grabbers, the Axion family does not swap firmware on the fly (this is similar to the Cyton). The Axion is shipped with firmware that supports the latest Camera Link Specification and has been tested with all known cameras at the time of the release. However, new features may be added and anomalies will be corrected from time to time. These updates will take the form of a new firmware file (\*.fsh). You may receive an updated firmware file as part of support issue, or a new firmware release may be part of a new SDK. In general, it is best to update the firmware on your board whenever you upgrade to a major new version of the SDK.

To update the board's firmware, type to the following command in a console window:

**FWdownload**

follow the instruction of the download program.

Note: After the firmware download process is complete, you must power down your computer in order for the new firmware to become active.

AXN-1-10 BitFlow, Inc. Version A.3

# 1.4 Axion Camera Configuration Files

The Axion is the second member of BitFlow's Gen 2 family. These frame grabber all use an XML based camera configuration file. This differs from previous models of BitFlow's frame grabbers that have all used a binary proprietary file format (which mean they could only be edited using BitFlow's tools). The file format uses the extension "BFML" but is actually an XML file with an XML compliant schema. The schema file is installed automatically and is called "BFML.xsd".

BFML files can be edited in any text editor. User's familiar with XML will understand the format right away. Users not familiar with XML files should not have too much trouble editing the files; the XML file format is used everywhere and there are many resources available for learning the format. A dedicated XML file editor can also be used, this can sometimes simplify editing when used in association with a schema file. However, we recommend using our dedicated BFML file editor, CamML. This is installed automatically by the SDK installer.

The BFML file format is documented on BitFlow's website. Please see the BitFlow website downloads page for a link to the BFML documentation.

Note: The tools used to edit previous BitFlow camera configuration files (CamEd, CamVert) can not be used to edit BFML files.

#### 1.4.1 BFML Camera File Modes

Previous BitFlow camera configuration file only supported a single mode of camera operation. In order to support multiple (e.g. free-running, one-shot, triggered, encoder, etc.) modes for a given camera file, multiple files were required, one for each mode. The BFML file format can contain an unlimited number of camera modes. This makes things much simpler since only one file is needed for each model of camera. Then the different modes of operation are contained within that one BFML file.

Switching between camera modes is easy, this can be done via SysReg, with each of the camera modes are enumerated, and the user can pick which mode they want to use. The modes are also available from the API. There is a function to enumerate the modes and s function to switch modes on the fly.

Customer can create their own modes as they see fit. They can simple copy an existing mode and change to suite their needs. The new mode should have a new name (also the comment should be updated). Once this file is save, the mode will be available in SysReg as well as from the API.

The Axion Models

The Axion-CL

# 1.5 The Axion Models

There are five models of the Axion-CL. Table 1-1 illustrates the capabilities of each model.

Table 1-1 The Axion Models

| Capability                                 | AXN-PC2-<br>1xE | AXN-PC2-<br>2xE | AXN-PC2-<br>1xB | AXN-PC2-<br>2xB | AXN-PC2-<br>4xB |

|--------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Number of Base CL cameras supported        | 1               | 2               | 1               | 2               | 4               |

| Number of Medium CL cameras supported      | 1               | 2               | 0               | 0               | 0               |

| Number of Full CL cameras supported        | 1               | 2               | 0               | 0               | 0               |

| Number of 80-bit CL cameras supported      | 1               | 2               | 0               | 0               | 0               |

| Number of Virtual Frame Grabbers supported | 1               | 2               | 1               | 2               | 4               |

| Number of independent trigger inputs       | 1               | 2               | 1               | 2               | 4               |

| Number of independent encoder inputs       | 1               | 2               | 1               | 2               | 4               |

| Number of PCI configurations (devices)     | 1               | 2               | 1               | 2               | 4               |

| Maximum DMA bandwidth                      | 1.75 GB/S       |

AXN-1-12 BitFlow, Inc. Version A.3

# The StreamSync Acquisition Engine

# Chapter 2

#### 2.1 Introduction

The StreamSync system consists of an Acquisition Engine and a Buffer Manager. The StreamSync system was first released on the Cyton-CXP and is a departure from previous BitFlow frame grabbers. Subsequently it was ported to the Axion, and will be used on all new frame grabbers moving forward. The StreamSync system is a start-from-scratch complete redesign of the acquisition and DMA parts of a frame grabber. BitFlow used its years of experience in this area to design a next generation, super efficient capture system.

Currently the StreamSync engine is used on the Aon-CXP, the Axion-CL, Claxon-CXP, Claxon-FXP, and the Cyton-CXP.

From a software perspective, the StreamSync system is compatible with the previous BitFlow products. However, digging deeper, these new system have a lot more power and flexibility. These new features will be described in the following sections.

The StreamSync system has many improvements over previous systems. The main improvements are:

Efficient support for variable sized images with fast context switches between frames

Per frame control of acquisition properties (AOI specifically)

Hardware control of image sequencing

Enhanced debug capabilities

Efficient support for on-demand buffer allocation (GenlCam model)

Gracefully recovery from dropped packets (either on the input side or the DMA side)

This chapter describes the StreamSync Acquisition Engine while the next chapter describes the StreamSync Buffer Manager.

## 2.2 The StreamSync Acquisition Engine World

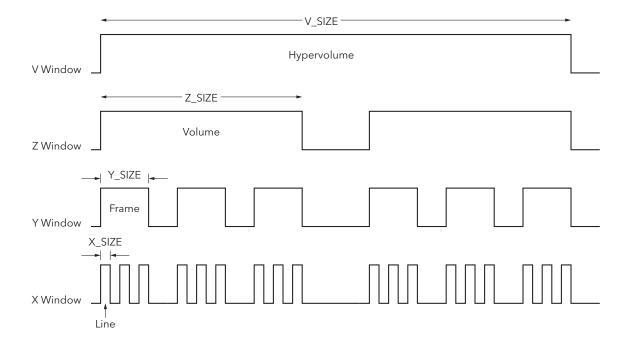

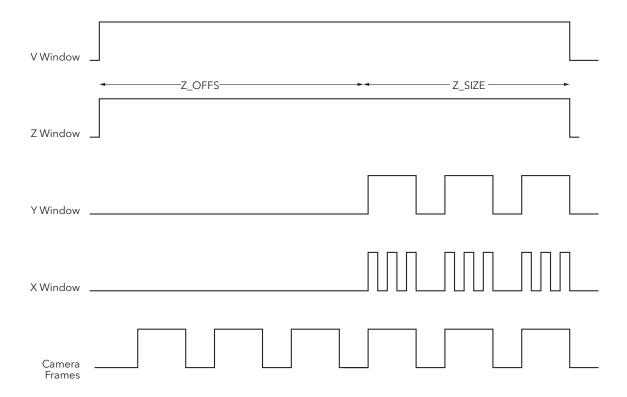

We are used to the concept that images have an X and a Y dimension. The Acquisition Engine expands on this concept by adding two further dimension Z and V. The Z dimension controls a sequence of frames or "Volume" of frames. The V dimension controls a sequence of volumes, or "Hypervolume". Figure 2-1 illustrates these concepts.

Figure 2-1 StreamSync Acquisition Engine Dimensions

The size of the X window, i.e. the number of pixels per line, is controlled by the X\_SIZE register. The size of the Y window, i.e. number of lines per frame, is controlled by the Y\_SIZE register. The size of the Z window, i.e. number of frames per volume, is controlled by the Z\_SIZE register. Finally, the size of the V window, i.e. number of volumes to acquire, is controlled by the V\_SIZE register. Note that the size of the Y window and the Z window can be dynamically controlled by external triggers, see below for more details.

### 2.2.1 Controlling the StreamSync Acquisition Engine

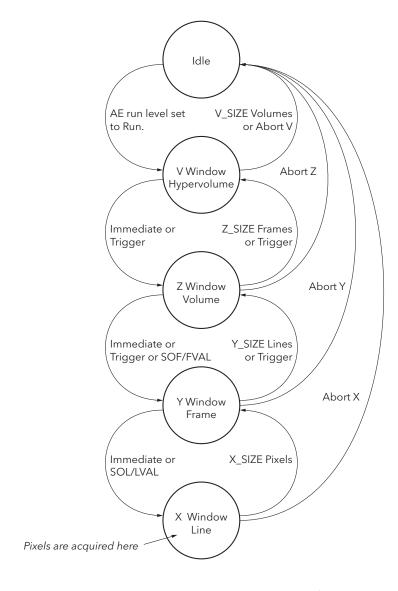

Acquisition of images is controlled by the AE\_RUN\_LEVEL register. The run level controls the conditions under which the Acquisition Engine will start or stop acquiring image data. Acquisition can be idle, which means nothing will be acquired, or it can be running, which means data will be acquired when the engine is inside the V, Z,Y and X windows. There are various conditions which control whether the engine is inside or outside of these windows.

Acquisition can be aborted on any X, Y, Z, or V boundary. The choice of boundary depends on whether one wants to abort immediate, which can cause acquisition of incomplete frames, or one wants to stop at the end of the line/frame/volume, which provides a more graceful end to acquisition.

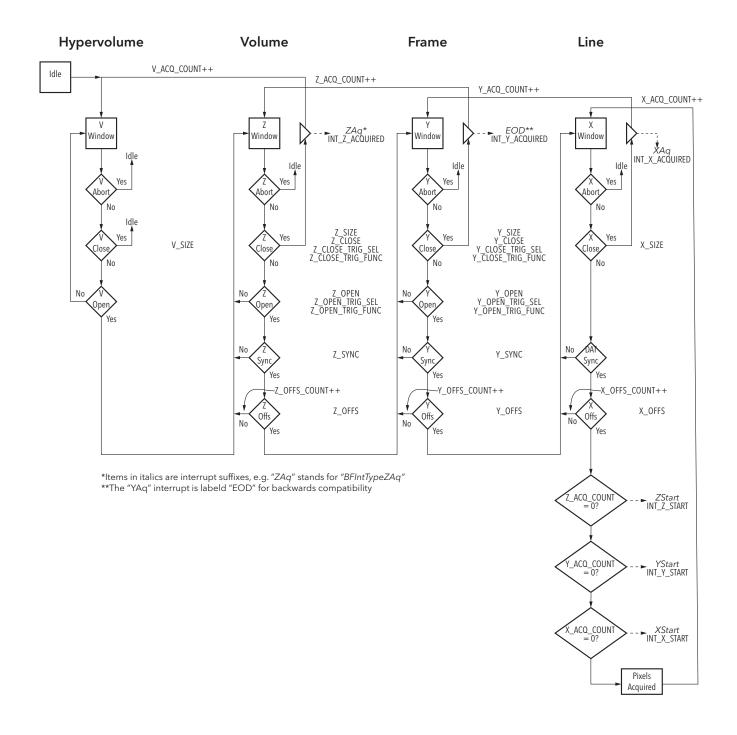

It's easiest to think of the Acquisition Engine level in terms of a state machine. When a window is "opened" the run level moves down to the next state below. When a window "closes", the run level moves to the state above. If the window at the top level closes, the run level goes to idle. Figure 2-2 illustrates this type of state machine:

Figure 2-2 Acquisition Engine Run Level

The action that causes a window to be opened or closed depends on the type of window. Some windows can be opened in more than one way. For example the Y window can be opened when a Start Of Frame (SOF) packet (or FVAL from a CL camera) is sent from the camera, or it can be opened by a trigger (all SOF packets are ignored

until the trigger condition is met) or it can just be opened immediately, as soon the Acquisition Engine level is inside the X window (i.e. the stat above). Table 2-1 enumerates all of these conditions..

Table 2-1 Open Close Conditions

| Window | Open                         | Close                          |

|--------|------------------------------|--------------------------------|

| V      | AE run level set to Run      | Abort V, V_SIZE volumes        |

| Z      | Trigger, Immediate           | Trigger, Abort Z, Z_SIZE frame |

| Υ      | Trigger, SOF/FVAL, Immediate | Trigger, Abort Y, Y_SIZE lines |

| Χ      | SOL/LVAL, Immediate          | Abort X, X_SIZE pixels         |

#### 2.2.2 Observing the StreamSync Acquisition Engine

The state of the Acquisition Engine can be observed at any time. The register AE\_LEVEL indicates the current run level of the Acquisition Engine. In other words, this register returns the current state as shown in Figure 2-2. While this is not very useful in a free-running situation, as the value will be changing constantly, it can be very helpful debugging if the system gets stuck (e.g. waiting for a trigger).

#### 2.2.3 Synchronizing the StreamSync Acquisition Engine With a CXP Camera

Normally acquisition is synchronized with camera by special CXP header packets called Start Of Frame (SOF) and Start Of Line (SOL). The Acquisition Engine will synchronize its Y window (frame) with the SOF and X window with the SOL. This means that all packets from the camera will be dropped until the SOF is seen (causing the Acquisition Engine to open the Y window), and then packets are further dropped until SOL must be seen (opening the X window). Each line requires an SOL packet. This process keeps the Acquisition Engine synchronized to the camera even if packets are dropped. This functionality can be enable/disable by the ZSYNC and YSYNC bits.

#### 2.2.4 Synchronizing the StreamSync Acquisition Engine With a Camera Link Camera

Normally acquisition is synchronized with camera by FVAL (Frame VALid) and the LVAL (Line VALid). The Acquisition Engine will synchronize its Y window (frame) with the FVAL and X window (line) with the LVAL. This means that all pixels from the camera will be dropped until the FVAL is seen (causing the Acquisition Engine to open the Y window), and then packets are further dropped until LVAL must be seen (opening the X window). Each line requires an LVAL edge. This process keeps the Acquisition Engine synchronized to the camera even if packets are dropped. This functionality can be enable/disable by the ZSYNC and YSYNC bits.

Note: For line scan camera, FVAL is not used and the Y Window will open either immediately in free-run mode, or based on a trigger eddge.

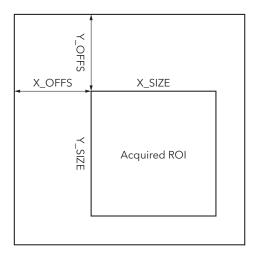

### 2.2.5 Regions Of Interest (ROI) with the StreamSync Acquisition Engine.

The Acquisition Engine support capturing a subwindow or ROI of the image that the camera is putting out. The Y\_SIZE and X\_SIZE registers control how many lines and pixels are acquired per frame, regardless of the actual frames size coming out of the camera. Further there are Y\_OFFS and X\_OFFS registers which can locate the subwindow anywhere inside of the camera's frame. These concepts are show in Figure 2-3.

Camera's Frame

Figure 2-3 Acquisition Engine ROI

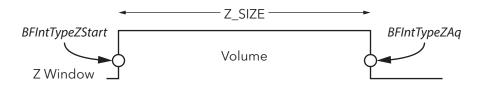

Similarly there is a Z\_OFFS register which if non-zero can cause the board to discard a certain number of frames before starting an acquisition of a sequence. This concept is illustrated in Figure 2-4.

Figure 2-4 Z\_OFFS Illustration

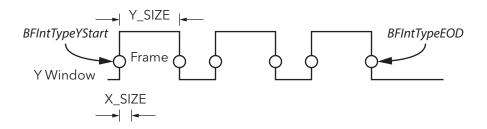

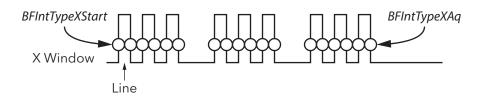

# 2.3 Window Interrupts

Interrupts at the start and end of each major window are available for use by host processes. The X, Y and Z windows (line, frame volume) all can provide interrupts. There are no interrupts for the V Window (hypervolume). Figure 2-5 Show the relationship between the interrupts and the acquisition Windows.

Note: The labels in italics in Figure 2-5 are are the actual interrupt names that can be used with the BitFlow SDK function calls.

Figure 2-5 X/Y/Z Interrupts

AE State Machine The Axion-CL

# 2.4 AE State Machine

Figure 2-6 AE State Machine

# 2.5 Triggering the StreamSync Acquisition Engine

One of the areas where the power of the Acquisition Engine is really seen is with regards to triggering. There are many more ways to use triggers in the Acquisition Engine. Primarily triggers can be used to "open" a window and/or to "close" a window. For example, a trigger could be used to start the acquisition of each frame and/or end the acquisition of each frame.

Further, a trigger could be use to start the acquisition of each volume (sequence of frames) and/or end the acquisition of a volume. Further flexibility comes from the fact that the source for each event (i.e. open or close) can be different or the same. This means a frame could be started with one trigger or ended with another, or the frame could start on the rising edge and end on the falling edge of the same trigger. Please refer to Figure 2-2 for more information on how a trigger can be used to change the state of the Acquisition Engine.

# 2.6 Comparing the StreamSync Acquisition Engine to Other BitFlow products

While the Acquisition Engine might seem very complex, it is actually quite simple to use and has considerably more power than previous acquisition engines used on all previous BitFlow frame grabbers. From a software point of view, the BitFlow API hides the differences between the traditional acquisition systems and the newer Acquisition Engine. However, for users that desire more flexibility and are willing to do some lower level coding, the Acquisition Engine can handle almost any acquisition scenario.

For users who were already doing some lower level programming using other BitFlow products, it's helpful to see how this new system relates to the tradition acquisition engine. Table 2-2 shows some examples of the traditional and the new system.

Table 2-2 Comparing Traditional and New Acquisition Systems

| Traditional<br>Command | X_SIZE       | Y_SIZE        | Z_SIZE | V_SIZE   | AE_RUN_<br>LEVEL |  |

|------------------------|--------------|---------------|--------|----------|------------------|--|

| Snap                   | Camera Width | Camera Height | 1      | 1        | Run              |  |

| Grab                   | Camera Width | Camera Height | 1      | 0xffffff | Run              |  |

| Grab N<br>frames       | Camera Width | Camera Height | N      | 1        | Run              |  |

| Freeze                 |              |               |        |          | Abort Z          |  |

| Abort                  |              |               |        |          | Abort X          |  |

AXN-2-10 BitFlow, Inc. Version A.3

# 2.7 AE\_CON

| Bit | Name          |

|-----|---------------|

| 0   | AE_RUN_LEVEL  |

| 1   | AE_RUN_LEVEL  |

| 2   | AE_RUN_LEVEL  |

| 3   | AE_RUN_LEVEL  |

| 4   | Reserved      |

| 5   | Reserved      |

| 6   | Reserved      |

| 7   | Reserved      |

| 8   | Reserved      |

| 9   | CLR_ACQ_COUNT |

| 10  | Reserved      |

| 11  | Reserved      |

| 12  | Reserved      |

| 13  | Reserved      |

| 14  | Reserved      |

| 15  | Reserved      |

| 16  | Reserved      |

| 17  | Reserved      |

| 18  | Reserved      |

| 19  | Reserved      |

| 20  | Reserved      |

| 21  | Reserved      |

| 22  | Reserved      |

| 23  | Reserved      |

| 24  | Reserved      |

| 25  | Reserved      |

| 26  | Reserved      |

| 27  | Reserved      |

| 28  | Reserved      |

| 29  | Reserved      |

| 30  | Reserved      |

| 31  | Reserved      |

AE CON The Axion-CL

#### AE\_RUN\_LEVEL

R/W, AE\_CON[3..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This is the main control for starting/aborting acquisition. Writing this register changes the current run level. Reading this register returns the current run level command (not the current status). The abort run levels exit acquisition on a clean boundary. V exits on a volume boundary, Z on a frame boundary, Y on a line boundary, X on a 128-byte data boundary.

| AE_RUN_LEVEL | Meaning                                              |

|--------------|------------------------------------------------------|

| 0 (0000b)    | System is idle                                       |

| 1 (0001b)    | Run - start running (i.e. acquiring)                 |

| 2 (0010b)    | Abort V - stop at the end of the next volume         |

| 3 (0011b)    | Abort Z - stop at the end of the next frame          |

| 4 (0100b)    | Abort Y - stop at the end of the next line           |

| 5 (0101b)    | Abort X - stop at the end of the next 128-byte block |

#### CLR\_ACQ\_ COUNT

RO, AE\_CON[9], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Write a 1 to this bitfield will reset to 0 the following registers V\_ACQ\_COUNT, Z\_ACQ\_COUNT, Y\_ACQ\_COUNT and X\_ACQ\_COUNT.

AXN-2-12 BitFlow, Inc. Version A.3

# 2.8 AE\_STATUS

| Bit | Name             |

|-----|------------------|

| 0   | AE_STATE         |

| 1   | AE_STATE         |

| 2   | AE_STATE         |

| 3   | Reserved         |

| 4   | AE_FIFO_OVERFLOW |

| 5   | Reserved         |

| 6   | Reserved         |

| 7   | Reserved         |

| 8   | Reserved         |

| 9   | Reserved         |

| 10  | Reserved         |

| 11  | Reserved         |

| 12  | Reserved         |

| 13  | Reserved         |

| 14  | Reserved         |

| 15  | Reserved         |

| 16  | Reserved         |

| 17  | Reserved         |

| 18  | Reserved         |

| 19  | Reserved         |

| 20  | Reserved         |

| 21  | Reserved         |

| 22  | Reserved         |

| 23  | Reserved         |

| 24  | Reserved         |

| 25  | Reserved         |

| 26  | Reserved         |

| 27  | Reserved         |

| 28  | Reserved         |

| 29  | Reserved         |

| 30  | Reserved         |

| 31  | Reserved         |

AE\_STATUS The Axion-CL

## **AE\_STATE**

RO, AE\_STATUS[2..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register indicates the current run level of the acquisition engine. The following table shows the meanings of each state.

| AE_STATE | Meaning                       |

|----------|-------------------------------|

| 0 (000b) | Idle - System is idle         |

| 1 (001b) | System is inside the V window |

| 2 (010b) | System is inside the Z window |

| 3 (011b) | System is inside the Y window |

| 4 (100b) | System is inside the X window |

## AE\_FIFO\_ OVERFLOW

RO, AE\_STATUS[4], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

If this bit is 1, the FIFO between acquisition engine and packet generation over-flowed. The acquisition engine will abort.

AXN-2-14 BitFlow, Inc. Version A.3

# 2.9 AE\_STREAM\_SEL

| Bit | Name                |

|-----|---------------------|

| 0   | STREAM_SEL          |

| 1   | STREAM_SEL          |

| 2   | STREAM_SEL          |

| 3   | STREAM_SEL          |

| 4   | STREAM_SEL          |

| 5   | STREAM_SEL          |

| 6   | STREAM_SEL          |

| 7   | STREAM_SEL          |

| 8   | Reserved            |

| 9   | Reserved            |

| 10  | Reserved            |

| 11  | Reserved            |

| 12  | Reserved            |

| 13  | Reserved            |

| 14  | Reserved            |

| 15  | Reserved            |

| 16  | Reserved            |

| 17  | Reserved            |

| 18  | Reserved            |

| 19  | Reserved            |

| 20  | Reserved            |

| 21  | Reserved            |

| 22  | Reserved            |

| 23  | Reserved            |

| 24  | Reserved            |

| 25  | Reserved            |

| 26  | Reserved            |

| 27  | Reserved            |

| 28  | Reserved            |

| 29  | Reserved            |

| 30  | Reserved            |

| 31  | USE_SYNTHETIC_FRAME |

AE\_STREAM\_SEL The Axion-CL

#### STREAM\_SEL

R/W, AE\_STREAM\_SEL[7..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Program this register to the stream aggregator that this acquisition engine should get its data from. Currently only the values 0 to 3 are supported. Generally this register should be programmed to correspond to the VFG number that is being used to access the acquisition engine. For example, for VFG1 set this register to 1.

## USE\_ SYNTHETIC\_ FRAME

R/W, AE\_STREAM\_SEL[31], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Use the Synthetic Frame generator instead of the camera.

AXN-2-16 BitFlow, Inc. Version A.3

# 2.10 V\_WIN\_DIM

| Bit | Name     |

|-----|----------|

| 0   | V_SIZE   |

| 1   | V_SIZE   |

| 2   | V_SIZE   |

| 3   | V_SIZE   |

| 4   | V_SIZE   |

| 5   | V_SIZE   |

| 6   | V_SIZE   |

| 7   | V_SIZE   |

| 8   | V_SIZE   |

| 9   | V_SIZE   |

| 10  | V_SIZE   |

| 11  | V_SIZE   |

| 12  | V_SIZE   |

| 13  | V_SIZE   |

| 14  | V_SIZE   |

| 15  | V_SIZE   |

| 16  | Reserved |

| 17  | Reserved |

| 18  | Reserved |

| 19  | Reserved |

| 20  | Reserved |

| 21  | Reserved |

| 22  | Reserved |

| 23  | Reserved |

| 24  | Reserved |

| 25  | Reserved |

| 26  | Reserved |

| 27  | Reserved |

| 28  | Reserved |

| 29  | Reserved |

| 30  | Reserved |

| 31  | Reserved |

V WIN DIM The Axion-CL

## **V\_SIZE**

R/W, V\_WIN\_DIM[15..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register defines size of the V window, that is, the number of volumes to acquire. A value of 0XFFFF means infinite. When set to infinite, the acquisition engine can be stopped by writing AE\_RUN\_LEVEL.

The most common setting for this field is either 1 or 0xFFFF.

This register is writable only when AE\_STATE is 0 (idle). Writes to this field will be ignored if AE\_STATE is not 0.

# 2.11 Z\_WIN\_CON

| Bit | Name              |

|-----|-------------------|

| 0   | Z_CLOSE_TRIG_FUNC |

| 1   | Z_CLOSE_TRIG_FUNC |

| 2   | Z_CLOSE_TRIG_FUNC |

| 3   | Z_CLOSE_TRIG_FUNC |

| 4   | Z_CLOSE_TRIG_SEL  |

| 5   | Z_CLOSE_TRIG_SEL  |

| 6   | Z_CLOSE_TRIG_SEL  |

| 7   | Z_CLOSE_TRIG_SEL  |

| 8   | Z_CLOSE           |

| 9   | Z_CLOSE           |

| 10  | Z_CLOSE           |

| 11  | Z_CLOSE           |

| 12  | Z_OPEN_TRIG_FUNC  |

| 13  | Z_OPEN_TRIG_FUNC  |

| 14  | Z_OPEN_TRIG_FUNC  |

| 15  | Z_OPEN_TRIG_FUNC  |

| 16  | Z_OPEN_TRIG_SEL   |

| 17  | Z_OPEN_TRIG_SEL   |

| 18  | Z_OPEN_TRIG_SEL   |

| 19  | Z_OPEN_TRIG_SEL   |

| 20  | Z_OPEN            |

| 21  | Z_OPEN            |

| 22  | Z_OPEN            |

| 23  | Z_OPEN            |

| 24  | Z_SYNC            |

| 25  | Z_SYNC            |

| 26  | Z_SYNC            |

| 27  | Z_SYNC            |

| 28  | Reserved          |

| 29  | Reserved          |

| 30  | Reserved          |

| 31  | Reserved          |

Z WIN CON The Axion-CL

#### Z\_CLOSE\_TRIG\_ FUNC

R/W, Z\_WIN\_CON[3..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register determines which trigger change (if any) will end the Z window.

| Z_CLOSE_TRIG_FUNC | Meaning                 |

|-------------------|-------------------------|

| 0 (0000b)         | Rising edge of trigger  |

| 1 (0001b)         | Falling edge of trigger |

| 2 (0010b)         | Trigger is high         |

| 3 (0011b)         | Trigger is low          |

| 4 (0100b)         | Either edge of trigger  |

#### Z\_CLOSE\_TRIG\_ SEL

R/W, Z\_WIN\_CON[7..4], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Selects which trigger will control the end the Z window.

| Z_CLOSE_TRIG_SEL | Meaning                                        |

|------------------|------------------------------------------------|

| 0 (0000b)        | The selected trigger (VFGx_TRIG_SEL)           |

| 1 (0001b)        | The selected encoder A (VFGx_ENCA_SEL)         |

| 2 (0010b)        | The selected encoder B (VFGx_ENCB_SEL)         |

| 3 (0011b)        | The selected encoder divider (VFGx_ENCDIV_SEL) |

| 4 (0100b)        | The selected encoder quad (VFGx_ENCQ_SEL)      |

#### **Z CLOSE**

R/W, Z\_WIN\_CON[11..8], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This field specifies how the Z window closes. Possible values are: 0 - size mode, 1 - trigger mode.

If size mode is specified, the acquisition engine waits for Z\_SIZE number of complete frames, it then closes the Z window and then checks to see if t are more volumes to acquire.

If trigger mode is specified, the trigger is selected by Z\_CLOSE\_TRIG\_SEL and the conditioning function is specified by Z\_CLOSE\_TRIG\_FUNC. The acquisition engine waits for the trigger condition to be satisfied, then continues acquiring to the next frame boundary, it then closes the Z window and then checks to see if t are more volumes to acquire.

AXN-2-20 BitFlow, Inc. Version A.3

#### Z\_OPEN\_TRIG\_ FUNC

R/W, Z\_WIN\_CON[15..12], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register determines which trigger change (if any) will start Z window.

| Z_OPEN_TRIG_FUNC | Meaning                 |

|------------------|-------------------------|

| 0 (0000b)        | Rising edge of trigger  |

| 1 (0001b)        | Falling edge of trigger |

| 2 (0010b)        | Trigger is high         |

| 3 (0011b)        | Trigger is low          |

| 4 (0100b)        | Either edge of trigger  |

### Z\_OPEN\_TRIG\_ SEL

R/W, Z\_WIN\_CON[19..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Selects which trigger will control the start Z window.

| Z_OPEN_TRIG_SEL | Meaning                                        |

|-----------------|------------------------------------------------|

| 0 (0000b)       | The selected trigger (VFGx_TRIG_SEL)           |

| 1 (0001b)       | The selected encoder A (VFGx_ENCA_SEL)         |

| 2 (0010b)       | The selected encoder B (VFGx_ENCB_SEL)         |

| 3 (0011b)       | The selected encoder divider (VFGx_ENCDIV_SEL) |

| 4 (0100b)       | The selected encoder quad (VFGx_ENCQ_SEL)      |

#### **Z\_OPEN**

R/W, Z\_WIN\_CON[23..20], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This field specifies how the Z window starts. Possible values are: 0 - immediate mode, 1 - trigger mode.

If immediate mode is specified, no trigger synchronization is required. The acquisition engine waits for any frame sync requirements, opens the Z window, then starts the setup of the Y window.

If trigger mode is specified, the trigger is selected by Z\_OPEN\_TRIG\_SEL and the conditioning function is specified by Z\_OPEN\_TRIG\_FUNC. The acquisition engine waits for the trigger condition to be satisfied, opens the Z window, then starts the setup of the Y window.

Z\_WIN\_CON The Axion-CL

## **Z\_SYNC**

$\mbox{R/W, Z\_WIN\_CON[}27..24\mbox{], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP}$

This field enforces the data-synchronization of streaming video to the acquisition engine for each individual frame in the z window. The following table shows explains this field.

| Z_SYNC | Meaning                                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | No synchronization. All streaming packets received after the Z Window are open will be acquired as part of the current frame.                                                                                                   |

| 1      | Start Of Frame (SOF) synchronization. All pixels received before the SOF will be ignored. This conditions is enforced for each frame in the Z window. On the Axion, SOF is generated by the FVAL signal coming from the camera. |

# 2.12 Z\_WIN\_DIM

| Bit | Name   |

|-----|--------|

| 0   | Z_SIZE |

| 1   | Z_SIZE |

| 2   | Z_SIZE |

| 3   | Z_SIZE |

| 4   | Z_SIZE |

| 5   | Z_SIZE |

| 6   | Z_SIZE |

| 7   | Z_SIZE |

| 8   | Z_SIZE |

| 9   | Z_SIZE |

| 10  | Z_SIZE |

| 11  | Z_SIZE |

| 12  | Z_SIZE |

| 13  | Z_SIZE |

| 14  | Z_SIZE |

| 15  | Z_SIZE |

| 16  | Z_OFFS |

| 17  | Z_OFFS |

| 18  | Z_OFFS |

| 19  | Z_OFFS |

| 20  | Z_OFFS |

| 21  | Z_OFFS |

| 22  | Z_OFFS |

| 23  | Z_OFFS |

| 24  | Z_OFFS |

| 25  | Z_OFFS |

| 26  | Z_OFFS |

| 27  | Z_OFFS |

| 28  | Z_OFFS |

| 29  | Z_OFFS |

| 30  | Z_OFFS |

| 31  | Z_OFFS |

Z WIN DIM The Axion-CL

#### **Z\_SIZE**

R/W, Z\_WIN\_DIM[15..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Number of frames (Y windows) to acquire per sequence (Z windows). The acquisition of frames will only start after Z\_OFFS frames have been skipped after the Z window is opened. Note this register is actually 24 bits, the upper 8 MSB are located in the Z\_SIZE\_MSB register.

#### **Z\_OFFS**

R/W, Z\_WIN\_DIM[31..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

The number of frames (Y windows) to skip before starting acquisition after the Z window has been opened. Note this register is actually 24 bits, the upper 8 MSB are located in the Z\_OFFS\_MSB register.

# 2.13 Z\_WIN\_DIM\_EXT

| Bit | Name       |

|-----|------------|

| 0   | Z_SIZE_MSB |

| 1   | Z_SIZE_MSB |

| 2   | Z_SIZE_MSB |

| 3   | Z_SIZE_MSB |

| 4   | Z_SIZE_MSB |

| 5   | Z_SIZE_MSB |

| 6   | Z_SIZE_MSB |

| 7   | Z_SIZE_MSB |

| 8   | Reserved   |

| 9   | Reserved   |

| 10  | Reserved   |

| 11  | Reserved   |

| 12  | Reserved   |

| 13  | Reserved   |

| 14  | Reserved   |

| 15  | Reserved   |

| 16  | Z_OFFS_MSB |

| 17  | Z_OFFS_MSB |

| 18  | Z_OFFS_MSB |

| 19  | Z_OFFS_MSB |

| 20  | Z_OFFS_MSB |

| 21  | Z_OFFS_MSB |

| 22  | Z_OFFS_MSB |

| 23  | Z_OFFS_MSB |

| 24  | Reserved   |

| 25  | Reserved   |

| 26  | Reserved   |

| 27  | Reserved   |

| 28  | Reserved   |

| 29  | Reserved   |

| 30  | Reserved   |

| 31  | Reserved   |

Z\_WIN\_DIM\_EXT The Axion-CL

**Z\_SIZE\_MSB** R/W, Z\_WIN\_DIM\_EXT[7..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the Z\_SIZE register by 8 more bits.

**Z\_OFFS\_MSB** R/W, Z\_WIN\_DIM\_EXT[23..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the Z\_OFFS register by 8 more bits.

AXN-2-26 BitFlow, Inc. Version A.3

# 2.14 Y\_INT\_DEC

| Bit | Name            |

|-----|-----------------|

| 0   | Y_INT_DEC_COUNT |

| 1   | Y_INT_DEC_COUNT |

| 2   | Y_INT_DEC_COUNT |

| 3   | Y_INT_DEC_COUNT |

| 4   | Y_INT_DEC_COUNT |

| 5   | Y_INT_DEC_COUNT |

| 6   | Y_INT_DEC_COUNT |

| 7   | Y_INT_DEC_COUNT |

| 8   | Y_INT_DEC_COUNT |

| 9   | Y_INT_DEC_COUNT |

| 10  | Y_INT_DEC_COUNT |

| 11  | Y_INT_DEC_COUNT |

| 12  | Y_INT_DEC_COUNT |

| 13  | Y_INT_DEC_COUNT |

| 14  | Y_INT_DEC_COUNT |

| 15  | Y_INT_DEC_COUNT |

| 16  | Reserved        |

| 17  | Reserved        |

| 18  | Reserved        |

| 19  | Reserved        |

| 20  | Reserved        |

| 21  | Reserved        |

| 22  | Reserved        |

| 23  | Reserved        |

| 24  | Reserved        |

| 25  | Reserved        |

| 26  | Reserved        |

| 27  | Reserved        |

| 28  | Y_INT_DEC_RST   |

| 29  | Y_INT_DEC_RST   |

| 30  | Y_INT_DEC_MODE  |

| 31  | Y_INT_DEC_MODE  |

|     |                 |

Y INT DEC The Axion-CL

### Y\_INT\_DEC\_ COUNT

R/W, Y\_INT\_DEC[15..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

When Y interrupt decimate mode is enable, the register determines the decimation amount. In other words, Y\_INT\_DEC\_COUNT interrupts must occur before the board emits a real interrupt.

### Y\_INT\_DEC\_RST

R/W, Y\_INT\_DEC[29..28], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Resets the Y interrupt decimation counter to 0.

## Y\_INT\_DEC\_ MODE

R/W, Y\_INT\_DEC[29..28], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register controls how Y interrupts are decimated.

| Y_DEC_MODE | Meaning                                       |

|------------|-----------------------------------------------|

| 0 (0000b)  | Y interrupts are not decimated                |

| 1 (0001b)  | Y interrupts are decimated by Y_INT_DEC_COUNT |

| 2 (0010b)  | reserved                                      |

| 3 (0011b)  | reserved                                      |

AXN-2-28 BitFlow, Inc. Version A.3

# 2.15 Y\_WIN\_CON

| Bit | Name              |

|-----|-------------------|

| 0   | Y_CLOSE_TRIG_FUNC |

| 1   | Y_CLOSE_TRIG_FUNC |

| 2   | Y_CLOSE_TRIG_FUNC |

| 3   | Y_CLOSE_TRIG_FUNC |

| 4   | Y_CLOSE_TRIG_SEL  |

| 5   | Y_CLOSE_TRIG_SEL  |

| 6   | Y_CLOSE_TRIG_SEL  |

| 7   | Y_CLOSE_TRIG_SEL  |

| 8   | Y_CLOSE           |

| 9   | Y_CLOSE           |

| 10  | Y_CLOSE           |

| 11  | Y_CLOSE           |

| 12  | Y_OPEN_TRIG_FUNC  |

| 13  | Y_OPEN_TRIG_FUNC  |

| 14  | Y_OPEN_TRIG_FUNC  |

| 15  | Y_OPEN_TRIG_FUNC  |

| 16  | Y_OPEN_TRIG_SEL   |

| 17  | Y_OPEN_TRIG_SEL   |

| 18  | Y_OPEN_TRIG_SEL   |

| 19  | Y_OPEN_TRIG_SEL   |

| 20  | Y_OPEN            |

| 21  | Y_OPEN            |

| 22  | Y_OPEN            |

| 23  | Y_OPEN            |

| 24  | Y_SYNC            |

| 25  | Y_SYNC            |

| 26  | Y_SYNC            |

| 27  | Y_SYNC            |

| 28  | Reserved          |

| 29  | Reserved          |

| 30  | Reserved          |

| 31  | Reserved          |

Y\_WIN\_CON The Axion-CL

#### Y\_CLOSE\_TRIG\_ FUNC

R/W, Y\_WIN\_CON[3..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register determines which trigger change (if any) will end the Y window.

| Y_CLOSE_TRIG_FUNC | Meaning                 |

|-------------------|-------------------------|

| 0 (0000b)         | Rising edge of trigger  |

| 1 (0001b)         | Falling edge of trigger |

| 2 (0010b)         | Trigger is high         |

| 3 (0011b)         | Trigger is low          |

| 4 (0100b)         | Either edge of trigger  |

#### Y\_CLOSE\_TRIG\_ SEL

R/W, Y\_WIN\_CON[7..4], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Selects which trigger will control the end the Y window.

| Y_CLOSE_TRIG_SEL | Meaning                                                     |

|------------------|-------------------------------------------------------------|

| 0 (0000b)        | The selected trigger (VFGx_TRIG_SEL)                        |

| 1 (0001b)        | The selected encoder A (VFGx_ENCA_SEL)                      |

| 2 (0010b)        | The selected encoder B (VFGx_ENCB_SEL)                      |

| 3 (0011b)        | The selected encoder divider (VFGx_ENCDIV_SEL)              |

| 4 (0100b)        | The selected encoder quad (VFGx_ENCQ_SEL)                   |

| 5 (0101b)        | The falling edge of FVAL will close the window (Axion only) |

#### Y CLOSE

R/W, Y\_WIN\_CON[11..8], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This field specifies how the Y window closes. Possible values are: 0 - size mode, 1 - trigger mode, 2 - size or trigger mode.

If  $Y\_CLOSE = 0$ , the acquisition engine waits for  $Y\_SIZE\_SIZE$  number of complete lines, it then closes the Y window and then checks to see if there are more frames to acquire.

If Y\_CLOSE = 1, the trigger is selected by Y\_CLOSE\_TRIG\_SEL and the conditioning function is specified by Y\_CLOSE\_TRIG\_FUNC. The acquisition engine waits for the trigger condition to be satisfied, then continues acquiring to the next line boundary, it then closes the Y window and then checks to see if there are more frames to acquire.

AXN-2-30 BitFlow, Inc. Version A.3

If Y\_CLOSE = 2, either condition above will close the window. Whichever conditions comes first will close the window (end the frame). This mode is used to acquire variable sized images where the trigger controls the frame size. Usually the rising edge of trigger opens the window (starts the frame) lines are acquired until either the trigger goes low, or Y\_SIZE lines have been acquired (i.e. the maximum frame size has been reached).

#### Y\_OPEN\_TRIG\_ FUNC

R/W, Y\_WIN\_CON[15..12], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This register determines which trigger change (if any) will start Y window.

| Y_OPEN_TRIG_FUNC | Meaning                 |

|------------------|-------------------------|

| 0 (0000b)        | Rising edge of trigger  |

| 1 (0001b)        | Falling edge of trigger |

| 2 (0010b)        | Trigger is high         |

| 3 (0011b)        | Trigger is low          |

| 4 (0100b)        | Either edge of trigger  |

#### Y\_OPEN\_TRIG\_ SEL

R/W, Y\_WIN\_CON[19..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Selects which trigger will control the start Y window.

| Y_OPEN_TRIG_SEL | Meaning                                        |

|-----------------|------------------------------------------------|

| 0 (0000b)       | The selected trigger (VFGx_TRIG_SEL)           |

| 1 (0001b)       | The selected encoder A (VFGx_ENCA_SEL)         |

| 2 (0010b)       | The selected encoder B (VFGx_ENCB_SEL)         |

| 3 (0011b)       | The selected encoder divider (VFGx_ENCDIV_SEL) |

| 4 (0100b)       | The selected encoder quad (VFGx_ENCQ_SEL)      |

#### Y\_OPEN

R/W, Y\_WIN\_CON[23..20], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This field specifies how the Y window starts. Possible values are: 0 - immediate mode, 1 - trigger mode.

If immediate mode is specified, no trigger synchronization is required. The acquisition engine waits for any line sync requirements, opens the Y window, then starts the setup of the X window.

Y WIN CON The Axion-CL

If trigger mode is specified, the trigger is selected by Y\_OPEN\_TRIG\_SEL and the conditioning function is specified by Y\_OPEN\_TRIG\_FUNC. The acquisition engine waits for the trigger condition to be satisfied, opens the Y window, then starts the setup of the X window.

## Y\_SYNC

R/W, Y\_WIN\_CON[27..24], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

This field enforces the data-synchronization of streaming video to the acquisition engine for each individual line in the y window. The following table explains this field.

| Y_SYNC | Meaning                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | No synchronization. All streaming packets received after the Y Window are open will be acquired as part of the current line.                                                                             |

| 1      | Start Of Line (SOL) synchronization. All pixels received before the SOL will be ignored. This conditions is enforced for each line in the Y window. On the Axion, SOL is generated from the LVAL signal. |

AXN-2-32 BitFlow, Inc. Version A.3

# 2.16 Y\_WIN\_DIM

| Bit | Name   |

|-----|--------|

| 0   | Y_SIZE |

| 1   | Y_SIZE |

| 2   | Y_SIZE |

| 3   | Y_SIZE |

| 4   | Y_SIZE |

| 5   | Y_SIZE |

| 6   | Y_SIZE |

| 7   | Y_SIZE |

| 8   | Y_SIZE |

| 9   | Y_SIZE |

| 10  | Y_SIZE |

| 11  | Y_SIZE |

| 12  | Y_SIZE |

| 13  | Y_SIZE |

| 14  | Y_SIZE |

| 15  | Y_SIZE |

| 16  | Y_OFFS |

| 17  | Y_OFFS |

| 18  | Y_OFFS |

| 19  | Y_OFFS |

| 20  | Y_OFFS |

| 21  | Y_OFFS |

| 22  | Y_OFFS |

| 23  | Y_OFFS |

| 24  | Y_OFFS |

| 25  | Y_OFFS |

| 26  | Y_OFFS |

| 27  | Y_OFFS |

| 28  | Y_OFFS |

| 29  | Y_OFFS |

| 30  | Y_OFFS |

| 31  | Y_OFFS |

Y\_WIN\_DIM The Axion-CL

**Y\_SIZE** R/W, Y\_WIN\_DIM[15..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Number of lines per frame (Y window) to acquire. This number is only acquired after the Y window is opened and after Y\_OFFS lines have been skipped.

**Y\_OFFS** R/W, Y\_WIN\_DIM[31..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Number of lines to skip before starting the acquisition of lines (after the Y windows is opened).

# 2.17 Y\_WIN\_DIM\_EXT

| Bit | Name       |

|-----|------------|

| 0   | Y_SIZE_MSB |

| 1   | Y_SIZE_MSB |

| 2   | Y_SIZE_MSB |

| 3   | Y_SIZE_MSB |

| 4   | Y_SIZE_MSB |

| 5   | Y_SIZE_MSB |

| 6   | Y_SIZE_MSB |

| 7   | Y_SIZE_MSB |

| 8   | Reserved   |

| 9   | Reserved   |

| 10  | Reserved   |

| 11  | Reserved   |

| 12  | Reserved   |

| 13  | Reserved   |

| 14  | Reserved   |

| 15  | Reserved   |

| 16  | Y_OFFS_MSB |

| 17  | Y_OFFS_MSB |

| 18  | Y_OFFS_MSB |

| 19  | Y_OFFS_MSB |

| 20  | Y_OFFS_MSB |

| 21  | Y_OFFS_MSB |

| 22  | Y_OFFS_MSB |

| 23  | Y_OFFS_MSB |

| 24  | Reserved   |

| 25  | Reserved   |

| 26  | Reserved   |

| 27  | Reserved   |

| 28  | Reserved   |

| 29  | Reserved   |

| 30  | Reserved   |

| 31  | Reserved   |

Y\_WIN\_DIM\_EXT The Axion-CL

Y\_SIZE\_MSB R/W, Y\_WIN\_DIM\_EXT[7..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the Y\_SIZE register by 8 more bits.

Y\_OFFS\_MSB R/W,Y\_WIN\_DIM\_EXT[23..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the Y\_OFFS register by 8 more bits.

AXN-2-36 BitFlow, Inc. Version A.3

# 2.18 X\_WIN\_DIM

| Bit | Name   |

|-----|--------|

| 0   | X_SIZE |

| 1   | X_SIZE |

| 2   | X_SIZE |

| 3   | X_SIZE |

| 4   | X_SIZE |

| 5   | X_SIZE |

| 6   | X_SIZE |

| 7   | X_SIZE |

| 8   | X_SIZE |

| 9   | X_SIZE |

| 10  | X_SIZE |

| 11  | X_SIZE |

| 12  | X_SIZE |

| 13  | X_SIZE |

| 14  | X_SIZE |

| 15  | X_SIZE |

| 16  | X_OFFS |

| 17  | X_OFFS |

| 18  | X_OFFS |

| 19  | X_OFFS |

| 20  | X_OFFS |

| 21  | X_OFFS |

| 22  | X_OFFS |

| 23  | X_OFFS |

| 24  | X_OFFS |

| 25  | X_OFFS |

| 26  | X_OFFS |

| 27  | X_OFFS |

| 28  | X_OFFS |

| 29  | X_OFFS |

| 30  | X_OFFS |

| 31  | X_OFFS |

X\_WIN\_DIM The Axion-CL

**X\_SIZE** R/W, X\_WIN\_DIM[15..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-

CXP

Number of 16-byte words to acquired per line (X window). This number is only acquired after the X window is opened and after X\_OFFS words have been skipped.

**X\_OFFS** R/W, X\_WIN\_DIM[31..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cy-

ton-CXP

Number of 16-byte words to skip per line (after the X window is opened).

# 2.19 X\_WIN\_DIM\_EXT

| Bit | Name        |

|-----|-------------|

| 0   | X_SIZE_MSB  |

| 1   | X_SIZE_MSB  |

| 2   | X_SIZE_MSB  |

| 3   | X_SIZE_MSB  |

| 4   | X_SIZE_MSB  |

| 5   | X_SIZE_MSB  |

| 6   | X_SIZE_MSB  |

| 7   | X_SIZE_MSB  |

| 8   | Reserved    |

| 9   | Reserved    |

| 10  | Reserved    |

| 11  | Reserved    |

| 12  | Reserved    |

| 13  | Reserved    |

| 14  | Reserved    |

| 15  | Reserved    |

| 16  | X_OFFS_MSB  |

| 17  | X_OFFS_MSB  |

| 18  | X_OFFS_MSB  |

| 19  | X_OFFS_MSB  |

| 20  | X_OFFS_MSB  |

| 21  | X_OFFS_MSB  |

| 22  | X_OFFS_MSB  |

| 23  | X_OFFS_MSB  |

| 24  | X_SHIFT     |

| 25  | X_SHIFT     |

| 26  | X_SHIFT     |

| 27  | X_SHIFT     |

| 28  | X_SHIFT     |

| 29  | X_SHIFT_DIR |

| 30  | Reserved    |

| 31  | Reserved    |

X WIN DIM EXT The Axion-CL

**X\_SIZE\_MSB** R/W, X\_WIN\_DIM\_EXT[7..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the X\_SIZE register by 8 more bits.

**X\_OFFS\_MSB** R/W,X\_WIN\_DIM\_EXT[23..16], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

Extends the X\_OFFS register by 8 more bits.

**X\_SHIFT** R/W,X\_WIN\_DIM\_EXT[24..18], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP,

Cyton-CXP

This register can be program to shift valid an image line left or right with respect to the start of LVAL (Camera Link) or SOL (CoaXPress). The units are pixels. To shift more

than 2^5, us the X\_OFFSET register. Use X\_SHIFT\_DIR to control the direction.

**X\_SHIFT\_DIR** R/W,X\_WIN\_DIM\_EXT[29], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cy-

ton-CXP

This bit controls the direction of the line shift set by the X\_SHIFT register.

AXN-2-40 BitFlow, Inc. Version A.3

## 2.20 V\_ACQUIRED

| Bit | Name                 |

|-----|----------------------|

| 0   | V_ACQ_COUNT          |

| 1   | V_ACQ_COUNT          |

| 2   | V_ACQ_COUNT          |

| 3   | V_ACQ_COUNT          |

| 4   | V_ACQ_COUNT          |

| 5   | V_ACQ_COUNT          |

| 6   | V_ACQ_COUNT          |

| 7   | V_ACQ_COUNT          |

| 8   | V_ACQ_COUNT          |

| 9   | V_ACQ_COUNT          |

| 10  | V_ACQ_COUNT          |

| 11  | V_ACQ_COUNT          |

| 12  | V_ACQ_COUNT          |

| 13  | V_ACQ_COUNT          |

| 14  | V_ACQ_COUNT          |

| 15  | V_ACQ_COUNT          |

| 16  | V_ACQ_COUNT          |

| 17  | V_ACQ_COUNT          |

| 18  | V_ACQ_COUNT          |

| 19  | V_ACQ_COUNT          |

| 20  | V_ACQ_COUNT          |

| 21  | V_ACQ_COUNT          |

| 22  | V_ACQ_COUNT          |

| 23  | V_ACQ_COUNT          |

| 24  | Reserved             |

| 25  | Reserved             |

| 26  | Reserved             |

| 27  | Reserved             |

| 28  | V_ACQ_COUNT_CLR_MODE |

| 29  | V_ACQ_COUNT_CLR_MODE |

| 30  | V_ACQ_COUNT_UPD_MODE |

| 31  | V_ACQ_COUNT_UPD_MODE |

Note: The V\_ACQUIRED register is not currently implemented

V ACQUIRED The Axion-CL

### V\_ACQ\_COUNT

R/W, V\_ACQUIRED[23..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Returns the total number of volumes (frame sequence) acquired since the last reset of this register. The behavior of this register when it reaches it maximum value depends on the register V\_ACQ\_COUNT\_CLEAR\_MODE. This register can be written to 0 by software at any time.

# CLR\_MODE

V\_ACQ\_COUNT\_ R/W, V\_ACQUIRED[29..28], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Controls how the V\_ACQ\_COUNT register is cleared.

| V_ACQ_COUNT_CLR_MODE | Meaning                                 |

|----------------------|-----------------------------------------|

| 0 (00b)              | Clear count on the start of acquisition |

| 1 (01b)              | Clear count on the start of V Window    |

| 2 (10b)              | Clear count on the start of Z Window    |

| 3 (11b)              | Clear count on the start of Y Window    |

# UPD\_MODE

**V\_ACQ\_COUNT\_** R/W, V\_ACQUIRED[31..30], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Controls when the V\_ACQ\_COUNT register is update.

| V_ACQ_COUNT_UPD_MODE | Meaning                |

|----------------------|------------------------|

| 0 (00b)              | Update continuously    |

| 1 (01b)              | Update end of V Window |

| 2 (10b)              | Update end of Z Window |

| 3 (11b)              | Update end of Y Window |

AXN-2-42 BitFlow, Inc. Version A.3

## 2.21 Z\_ACQUIRED

| Bit | Name                 |

|-----|----------------------|

| 0   | Z_ACQ_COUNT          |

| 1   | Z_ACQ_COUNT          |

| 2   | Z_ACQ_COUNT          |

| 3   | Z_ACQ_COUNT          |

| 4   | Z_ACQ_COUNT          |

| 5   | Z_ACQ_COUNT          |

| 6   | Z_ACQ_COUNT          |

| 7   | Z_ACQ_COUNT          |

| 8   | Z_ACQ_COUNT          |

| 9   | Z_ACQ_COUNT          |

| 10  | Z_ACQ_COUNT          |

| 11  | Z_ACQ_COUNT          |

| 12  | Z_ACQ_COUNT          |

| 13  | Z_ACQ_COUNT          |

| 14  | Z_ACQ_COUNT          |

| 15  | Z_ACQ_COUNT          |

| 16  | Z_ACQ_COUNT          |

| 17  | Z_ACQ_COUNT          |

| 18  | Z_ACQ_COUNT          |

| 19  | Z_ACQ_COUNT          |

| 20  | Z_ACQ_COUNT          |

| 21  | Z_ACQ_COUNT          |

| 22  | Z_ACQ_COUNT          |

| 23  | Z_ACQ_COUNT          |

| 24  | Reserved             |

| 25  | Reserved             |

| 26  | Reserved             |

| 27  | Reserved             |

| 28  | Z_ACQ_COUNT_CLR_MODE |

| 29  | Z_ACQ_COUNT_CLR_MODE |

| 30  | Z_ACQ_COUNT_UPD_MODE |

| 31  | Z_ACQ_COUNT_UPD_MODE |

Z ACQUIRED The Axion-CL

### **Z\_ACQ\_COUNT**

R/W, Z\_ACQUIRED[23..0], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Returns the total number of frames acquired since the last reset of this register. The behavior of this register when it reaches it maximum value depends on the register Z\_ ACQ\_COUNT\_CLEAR\_MODE. This register can be written to 0 by software at any time.

## Z\_ACQ\_COUNT\_ CLR\_MODE

R/W, Z\_ACQUIRED[29..28], Aon-CXP, Axion-CL, Claxon-CXP, Claxon-FXP, Cyton-CXP

Controls how the Z\_ACQ\_COUNT register is cleared.

| Z_ACQ_COUNT_CLR_MODE | Meaning                                 |

|----------------------|-----------------------------------------|

| 0 (00b)              | Clear count on the start of acquisition |

| 1 (01b)              | Clear count on the start of Z Window    |