# The BitBox

# **Hardware Reference Manual**

BitFlow, Inc. 400 West Cummings Park, Suite 5050 Woburn, MA 01801 USA Tel: 781-932-2900 Fax: 781-933-9965 Email: support@bitflow.com Web: www.bitflow.com Revision 1.0

### © 2016 BitFlow, Inc. All Rights Reserved.

This document, in whole or in part, may not be copied, photocopied, reproduced, translated or reduced to any other electronic medium or machine readable form without the prior written consent of BitFlow, Inc.

BitFlow, Inc. makes no implicit warranty for the use of its products and assumes no responsibility for any errors that may appear in this document, nor does it make a commitment to update the information contained herein.

BitFlow, Inc. retains the right to make changes to these specifications at any time without notice.

All trademarks are properties of their respective holders.

Revision History:

| Revision | Date       | Comments          |

|----------|------------|-------------------|

| A.0      | 2016-09-27 | First release     |

| A.1      | 2016-10-01 | Minor Corrections |

# **Table of Contents**

# P - Preface

Purpose BBX-P-1 Support Services BBX-P-1 Technical Support BBX-P-1 Sales Support BBX-P-1 Conventions BBX-P-2 Bitfield definitions BBX-P-3 Example Bitfield Definition BBX-P-3 Bitfield Definition Explanation. BBX-P-3

# 1 - General Description and Architecture

The BitBox BBX-1-1 Input and Output Signal Types BBX-1-2 Connection Signals BBX-1-2 Minimum Requirements BBX-1-3 Wiring the BitBox BBX-1-4 Wiring The 12-Pin Block Connectors BBX-1-4 Inserting/Removing 12-Pin Block Connectors BBX-1-5 BitBox Cables BBX-1-6 BitBox Signal Routing BBX-1-7 Input Signal Routing BBX-1-7 Output Signal Routing BBX-1-7

# 2 - BitBox Electrical Interfacing

The BitBox Inputs and Outputs BBX-2-1 The TTL inputs BBX-2-2 The TTL Outputs BBX-2-4 The Differential Inputs BBX-2-5 The Differential Outputs BBX-2-6 The Optocoupler Inputs BBX-2-7 The Optocoupler Outputs BBX-2-9 The 24V Inputs BBX-2-11 The Open Collector Outputs BBX-2-13

# **3 - Timing Sequencer**

Introduction BBX-3-1 The Auxiliary Timing Sequencer BBX-3-1 Description BBX-3-1 TS\_CONTROL BBX-3-3 TS\_TABLE\_CONTROL BBX-3-6 TS\_TABLE\_ENTRY BBX-3-8 ATS\_CONTROL BBX-3-11 ATS\_TABLE\_CONTROL BBX-3-14 ATS\_TABLE\_ENTRY BBX-3-16

# 4 - The Cyton And Axion I/O System

Introduction BBX-4-1 Concepts BBX-4-1 I/O Between Virtual Frame Grabbers BBX-4-1 Overview of the Cyton and Axion I/O System Routing BBX-4-2 Input Selection BBX-4-3 Internal Signals BBX-4-4 Output Signal Selection BBX-4-7 I/O Connector Output Signal Routing BBX-4-8 BitBox Output Signal Routing BBX-4-9

#### 5 - The Cyton and Axion I/O System Registers

Introduction BBX-5-1 CON60 BBX-5-2 CON61 BBX-5-4 CON62 BBX-5-6 CON63 BBX-5-10 CON64 BBX-5-15 ADDR\_TRIG\_FILTER BBX-5-19 ADDR\_ENCA\_FILTER BBX-5-21 ADDR\_ENCB\_FILTER BBX-5-23 BOX\_OUT\_DYN\_SEL\_SET\_A BBX-5-25 BOX\_OUT\_DYN\_SEL\_SET\_B BBX-5-28 BOX\_OUT\_DYN\_SEL\_SET\_C BBX-5-30 BOX\_OUT\_MODE\_SET\_A BBX-5-32 BOX\_OUT\_MODE\_SET\_B BBX-5-37 BOX\_OUT\_MODE\_SET\_C BBX-5-42

#### 6 - BitBox Programming

Programming the BitBox BBX-6-1 BitBox Access from the Camera Configuration File BBX-6-2 Example: Selecting a BitBox Input as a Source For A VFG function BBX-6-2 Example: Routing a BitBox Input to the Camera BBX-6-3 Example: Setting BitBox Outputs To Static Values BBX-6-3 Example: Routing BitBox Inputs to BitBox Outputs BBX-6-4 Example: Setting BitBox Outputs To Dynamic Signal BBX-6-4 Controlling BitBox Routing From Software BBX-6-7 Setting the BitBox Outputs To Static Values BBX-6-7 Setting the BitBox Outputs to a Dynamic Source BBX-6-7 Switching Trigger Sources From Software (Register Access) BBX-6-8 Switching Trigger Sources From Software (API) BBX-6-8 Switching Encoder Sources From Software (API) BBX-6-9

### 7 - Specifications

Introduction BBX-7-1 BitBox Power Requirements BBX-7-2

#### 8 - Mechanical

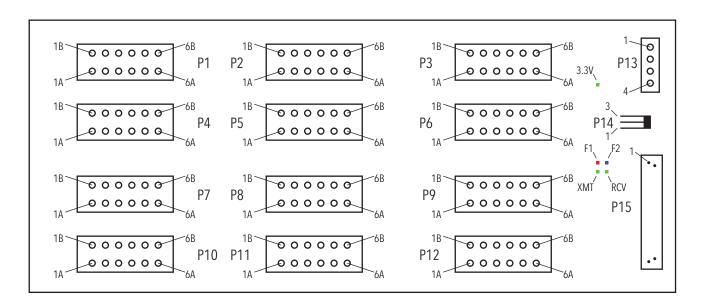

Introduction BBX-8-1 The BitBox Connectors BBX-8-2 Jumpers BBX-8-3 LEDs BBX-8-4 The Power Connector (P13) BBX-8-5 The Control Connector (P15) BBX-8-6 The Output Connectors P1 Through P6 BBX-8-7 The Input Connectors P7 Through P12 BBX-8-10 P7 Test Pins BBX-8-13

Table of Contents

# Preface

# Chapter P

# P.1 Purpose

This Hardware Reference Manual is intended for anyone using the BitBox general purpose I/O module. The purpose of this manual is two-fold. First, this manual completely describes how the module works. Second, it is a reference manual describing in detail the functionality of all of the registers on the associated frame grabber.

# P.1.1 Support Services

BitFlow, Inc. provides both sales and technical support for the BitBox family of products.

### P.1.2 Technical Support

Our web site is www.bitflow.com.

Technical support is available at 781-932-2900 from 9:00 AM to 6:00 PM Eastern Standard Time, Monday through Friday.

For technical support by email (support@bitflow.com) or by FAX (781-933-9965), please include the following:

Product name Camera type and mode being used Software revision number Computer CPU type, PCI chipset, bus speed Operating system Example code (if applicable)

#### P.1.3 Sales Support

Contact your local BitFlow Sales Representative, Dealer, or Distributor for information about how BitFlow can help you solve your most demanding camera interfacing problems. Refer to the BitFlow, Inc. web site (www.bitflow.com) for a list of North American representatives and worldwide distributors.

# P.1.4 Conventions

Table P-1 shows the conventions that are used for numerical notation in this manual.

#### Table P-1 Base Abbreviations

| Base        | Designator | Example |

|-------------|------------|---------|

| Binary      | b          | 1010b   |

| Decimal     | None       | 4223    |

| Hexidecimal | h          | 12fah   |

Table P-2 shows the numerical abbreviations that are used in this manual.

#### Table P-2 Numeric Abbreviations

| Abbreviation | Value   | Example |

|--------------|---------|---------|

| К            | 1024    | 256K    |

| Μ            | 1048576 | 1 M     |

# P.2 Bitfield definitions

# P.2.1 Example Bitfield Definition

Here is what each bitfield definition looks like:

BITFIELD R/W, CON0[7..0], Cyton-CXP, Axion-CL

Bitfield discussion.

# P.2.2 Bitfield Definition Explanation.

The definitions is broken into three sections (see Table P-3).

| Section             | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bitfield name       | This is the name of the bitfield. This name is used to pro-<br>gram this bitfield from software or from a camera configura-<br>tion file. When programming bitfields from software using a<br>BFRegPeek() or BFRegPoke() functions, the bitfield is pre-<br>ceded with "REG_". For example the bitfield CFREQ is<br>referred to in software as REG_CFREQ.                                                                                                                                                                                                                                                                                        |

| Bitfield details    | This section describes how the bitfield is accessed. The first<br>part describes how the bits can be accessed. For example<br>R/W means the register can be both read and written. See<br>theTable P-4 for details.The second part is the wide register<br>that the bitfield is located in. In the example above this bit-<br>field is in CON0. Following the wide register name is a bit-<br>field location description, in hardware engineering format.<br>For example, [70], means the bitfield has 8 bits, location in<br>positions 0 to 7. Finally this section also indicates if the reg-<br>ister is specific to only one product family. |

| Bitfield discussion | This section explains the purpose of the bitfield in detail.<br>Usually the meaning of every possible value of the bitfield is<br>listed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table P-4 explains the abbreviations used in the bitfield definitions.

#### Table P-4 Abbreviations

| Access     | Meaning                                                                             |

|------------|-------------------------------------------------------------------------------------|

| R/W        | Bitfield can be read and written.                                                   |

| RO         | Bitfield can only be read. Writing to this bit has no effect.                       |

| WO         | Bitfield can only be written. Reading from this bit will return meaningless values. |

| Karbon-CL  | This bitfield is functional only on the Karbon-CL.                                  |

| Karbon-CXP | This bitfield is functional only on the Karbon-CXP.                                 |

| Neon       | This bitfield is functional only on the Neon                                        |

| R64        | This bitfield is functional only on the R64 family.                                 |

| Alta       | This bitfield is functional only on the Alta family.                                |

| Cyton-CXP  | This bitfield is functional only on the Cyton-CXP family                            |

| Axion-CL   | This bitfield is functional only on the Axion-CL family                             |

# **General Description and Architecture**

# Chapter 1

# 1.1 The BitBox

The purpose of this chapter is to explain, at a block diagram level, how the BitBox works. Currently there is just one model in the BitBox family:

IOB-ISO35-C144 - I/O module, ISO DIN 35 rail mount, 144 pins

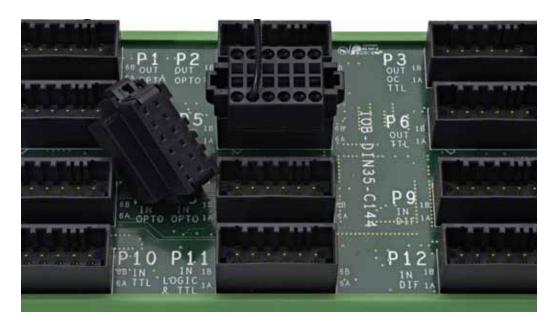

Figure 1-1 The BitBox

The BitBox is a general purpose I/O module that extends the I/O capabilities of the frame grabber and hence the PC. The target application space is complex machine vision system that require a large number of controls signals going to an from the host application. The usual solution is to buy general purpose I/O board, and run a large cable from the "rail" and other devices to the huge connector on the back of the PC. The BitBox solves a number of problems with this approach. It breaks out the signals right on the rail. It uses a small low cost cable to bring the signals to the PC. Finally, it uses the frame grabber that is already in the system as a host controller, no need to buy another board just for I/O!

The BitBox offers 36 fully programmable inputs and outputs in various electrical formats (e.g. TTL, Differential, etc). The BitBox inputs can be routed to various destinations on the frame grabber. They can cause interrupts, trigger cameras or other device. The level of every input can be read at any time by the host software (via registers on the frame grabber). The outputs can be driver by a number of different sources. They can be driven by programmable wave form generators, they can be driven from other inputs, they can be driven by static register that can be toggled by host software at any time.

The BitBox inputs and outputs are controlled by a small standard cable the goes from the frame grabber to the BitBox. Even though BitBox can simultaneously manage 72 signals, the cable between the BitBox and the frame grabber has only 15 wires.

### 1.1.1 Input and Output Signal Types

The BitBox has four types of inputs:

TTL Differential (LVDS) Optocoupler 24 V

The BitBox has four types of outputs:

TTL Differential (RS-422) Optocoupler Open Collector

#### 1.1.2 Connection Signals

All of the inputs and all of the outputs are simultaneously available. The user can mix and match I/O signal types as needed by their applications.

The I/O connectors on the BitBox are grouped in blocks of 12 signals. Each block of 12 takes a 12-pin block connector. This makes wire harness fabrication much easier as the harness can be built away from the machine chassis, and connected to the BitBox at final system assembly. The 12-pin block connectors use a screw-less friction system that makes inserting and removing wires quick and simple.

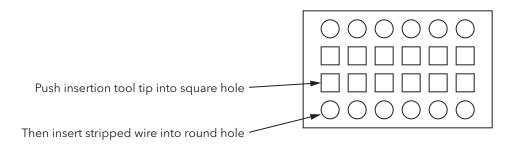

Figure 1-2 12-Pin Block Connectors

Power for the BitBox can come from one of two sources. It can come from a local power source that provides between 5 to 24 volts. Alternatively, it can come from the PC via the control cable. The control cable, in addition to carrying the control signals, can also carry power. Power in this case is provided by the PC's internal power supply.

# 1.1.3 Minimum Requirements

The minimum components required to use the BitBox are:

A cable between the BitBox and the PC

- At least one 12-pin block connector

- A BitFlow Cyton or Axion frame grabber.

- A power source (direct or via the frame grabber)

These components are explained in further detail in later sections of this manual

# 1.2 Wiring the BitBox

Wiring the BitBox is quite simple. The following subsections describe all that is needed:

### 1.2.1 Wiring The 12-Pin Block Connectors

First you must determine to which BitBox input or output each of your signals will be connected. Then determine which 12-signal block each belongs to. You can wire each of these groups to one 12-pin block connector.

Note: These support wire sizes from 20 to 26.

Adding a wire to one of these block connectors is easy:

Push the tip of the insertion tool into the square hole Push the stripped end the wire into the nearest round hole Remove insertion tool

Figure 1-3 illustrates the locations of these holes

#### Figure 1-3 12-Pin Block Connector Wire Insertion

To remove a wire, simply re-insert the tip of the insertion tool, and pull the associate wire out.

Note: The insertion tool part number is ACC-BOX-2.5-50 and is available from BitFlow.

Note: The 12-pin block connectors are part number CONN-BOX-IO12 and are available from BitFlow.

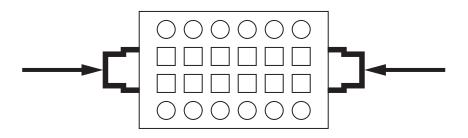

# 1.2.2 Inserting/Removing 12-Pin Block Connectors

To insert the 12-pin block connectors into the BitBox, simply push the connectors into the appropriate mating socket. The connectors are key so it is not possible to put the connectors in the wrong way.

To remove the 12-pint block connectors from the BitBox, squeeze the two sides of the connector (see Figure 1-4) and pull firmware away from the BitBox.

Figure 1-4 Removing 12-Pin Block Connectors

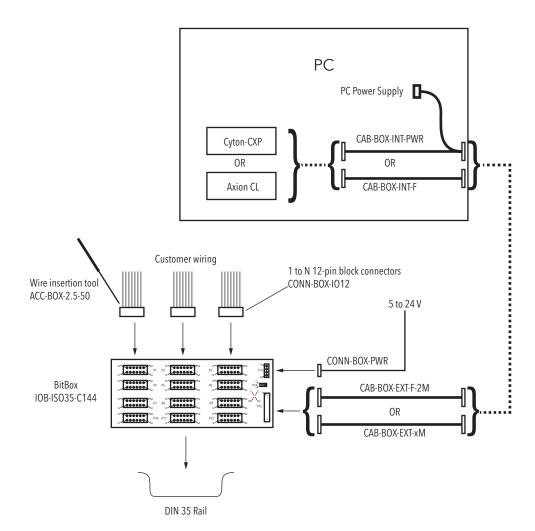

# 1.3 BitBox Cables

There are a number of cabling option available to connect the BitBox to the frame grabber in your PC. Low cost ribbon cables can be used for development environments or when the distance between the PC and the BitBox is small and there is relatively little risk of electrical interference. For longer distances and in electrically noisy environments, shielded cable that runs all the signals on twisted pair conductors is recommended. In addition, a power cable is needed, either directly to the box or internally from the PC. Figure 1-5 illustrates all of the cable options and how they are interconnected.

Note: All of the cables shown below are availale from BitFlow. In adition, wiring diagrams are available for customers who wish to fabricate their own cables.

Figure 1-5 BitBox Cable Configurations

# 1.4 BitBox Signal Routing

### 1.4.1 Input Signal Routing

The BitBox Inputs can be routed to a number of different destinations on the frame grabber. For more details please see Section 4.3. Each input's level can be read at anytime by software peeking the corresponding bitfield. See Section 5.1 for bitfield names that correspond to each input. In addition, every Bitbox input can be routed to any of the internal signals on any VFG. The list of internal signals is as follows:

VFGx\_TRIG\_SEL VFGx\_ENCA\_SEL VFGx\_ENCB\_SEL VFGx\_ENCDIV\_SEL VFGx\_ENCQ\_SEL

Each of these signals can be used in a variety of ways. They can trigger acquisition, they can trigger the timing sequencer, they can be sent to the camera or they can be sent back off the frame grabber to an output inside the PC (on the frame grabbers own I/O connector) or an output on the BitBox. The routing is controlled by the frame grabbers registers. Please see Section 5.1 for more information on the individual control registers.

### 1.4.2 Output Signal Routing

Each BitBox output can be driven by a number of different sources. There is a simple register for each output that can force the output to a high or low state. This same register can also be set to drive the output from a dynamic source. For each output there are a few choices for the dynamic source:

VFG0\_CCx VFG1\_CCx VFG2\_CCx VFG3\_CCx VFG0\_ATS\_CTx

Please see the Table 5-1 for a complete list.

Each VFG has four dynamic CCx signals: CC1, CC2, CC3 and CC4. Please see Section 4.5 on more information on these signals. In addition, VFG0 has four more dynamic signals VFG0\_ATS\_CT0, VFG0\_ATS\_CT1, VFG0\_ATS\_CT2 and VFG0\_ATS\_CT3. See Section 3.1.1 for more information on these signals. Not all models of Cytons and Axions have four VFGs, therefore on some models, not all of the dynamic sources will be available. However, all models of frame grabbers will have at least VFG0\_CCx and VFG0\_BCTx.

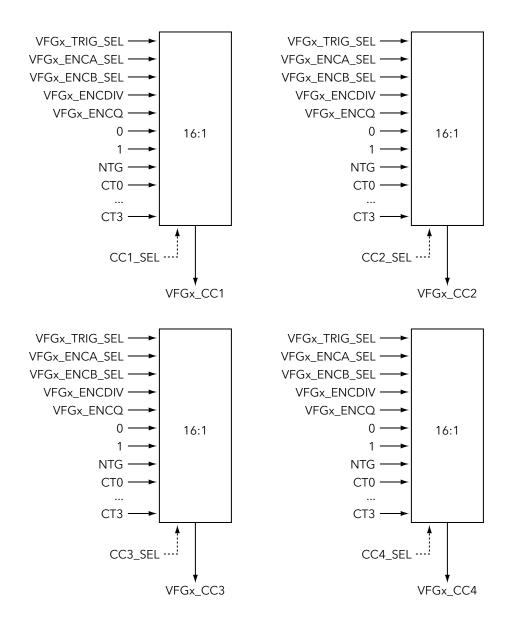

The CCx signals can, in turn, be driven by a number of different sources. For example, they can be driven by a Timing Sequencer (TS) which can create programmable wave forms, they can be driver by just about any of the inputs (which can also be coming from the BitBox). Please see Section Figure 4-7 for more information on how these signals can be routed.

The routing of these output signals is controlled by a set of registers on the frame grabber, please see Section 5.1 for more information on how to route these registers.

# **BitBox Electrical Interfacing**

# Chapter 2

# 2.1 The BitBox Inputs and Outputs

The BitBox has four types of inputs :

TTL Differential (LVDS) Optocoupler 24 V

The BitBox has four types of outputs:

TTL Differential (RS-422) Optocoupler Open Collector

This chapter provides details on the recommend ways to electrically interface to these inputs and output.

# 2.2 The TTL inputs

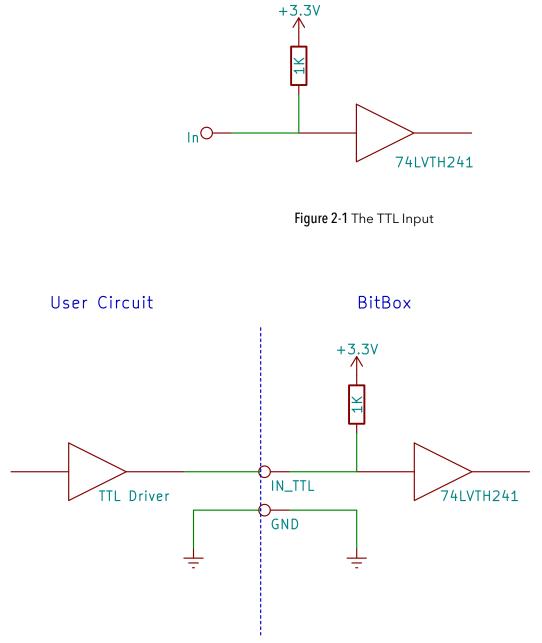

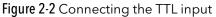

The TTL input uses a 74LVTH241 (see Figure 2-1). The input has a 1K pullup to 3.3V, see figure 1. If the input is unconnected, it will read1. Figure 2-2 shows how to connect a TTL driver to the BitBox TTL input. The BitBox and the user's grounds (GND) must be connected.

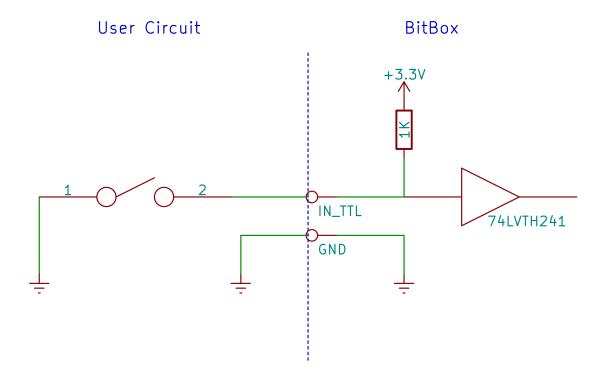

The pullup will allow an easy connection of a mechanical closure circuit, see Figure 2-3. It is recommended that the user applies a filter on that IO to clean up the mechanical chatter. See the registers TRIG\_FILTER, ENCA\_FILTER and ENCB\_FILTER in Section 5.1.

Figure 2-3 Connecting a closure element to the TTL input

# 2.3 The TTL Outputs

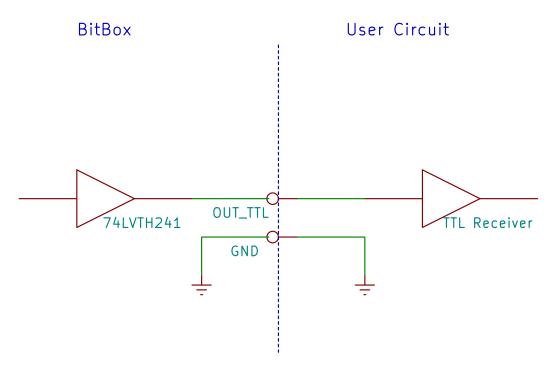

The TTL output is implemented with a 74LVTH241 (see Figure 2-4). Figure 2-5 shows how to connect the TTL output. The user's and the BitBox's grounds (GND) must be connected.

Figure 2-4 The TTL Output

Figure 2-5 Connecting the TTL Output

# 2.4 The Differential Inputs

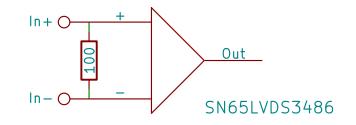

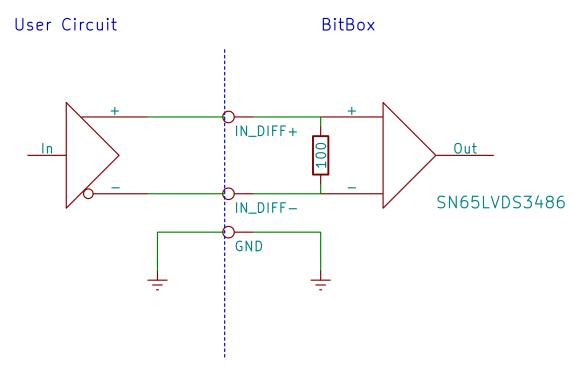

The differential inputs are implemented with a SN65LVDS3486, which are RS644. They have a 100 Ohm termination, see Figure 2-6. Figure 2-7 shows the connection of the differential receiver. The user's and the BitBox GNDs must be connected.

Figure 2-6 The Differential Receivers

Figure 2-7 Connecting the Differential Receivers

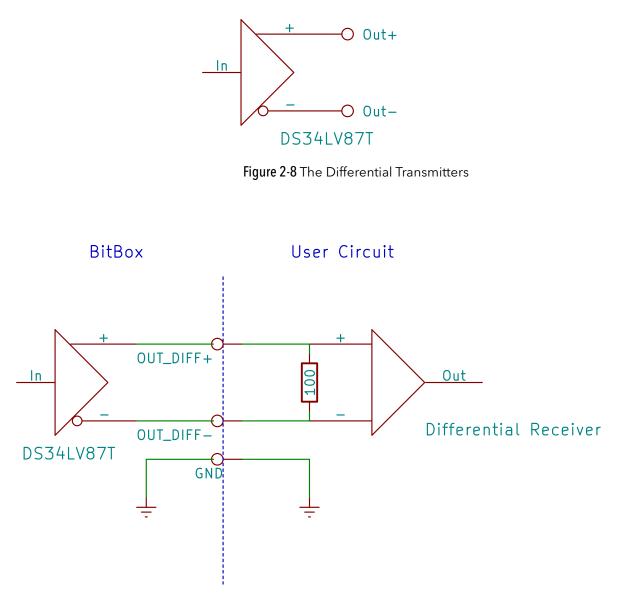

# 2.5 The Differential Outputs

The differential outputs are implemented with a DS34LV87T, which are RS422, see Figure 2-8. Figure 2-9 shows how to connect the differential outputs. The user's and the BitBox GNDs must be connected. The user should have a 100 Ohm termination.

Figure 2-9 Connecting The Differential Transmitters

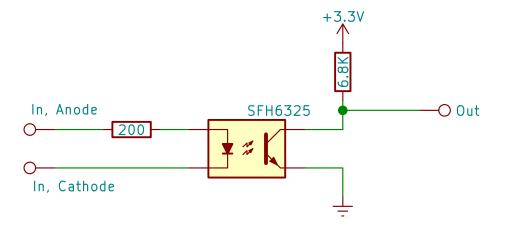

# 2.6 The Optocoupler Inputs

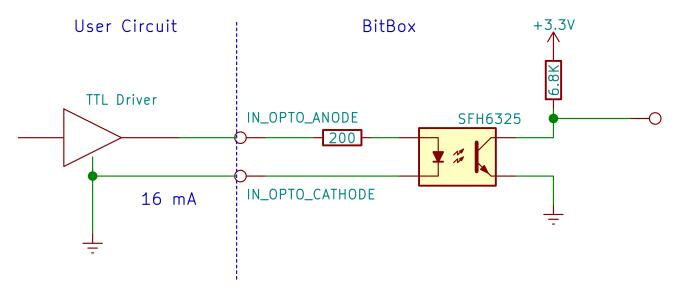

The opto input has been implemented with a Vishay SFH6325, see Figure 2-10. The user has access to the anode and the cathode of the input circuit. There is a 200 Ohm resistor in series with the anode. This resistor will limit the current through the input photodiode Warning: care must be exercised when driving the photodiode. The maximum current allowable through the photodiode is 25mA. That means that the maximum allowable voltage on the anode is 5V. Figure 2-11 shows a simple TTL circuit that drives the optocoupler input. The 'HI' of the 74LVTH241 will be ~3.3V. That will result in a current of ~16mA through the photodiode.

The user's TTL driver is connected to the anode input. The GND of the user's TTL driver is connected to the cathode. The user's TTL driver will drive a current through the photodiode. This same current returns to the user's GND through the cathode. The current that flows through the photodiode will generate light inside that photocoupler. This light will induce a current through the output transistor. The key to this circuit is that there is no galvanic connection between the user's circuit and the BitBox. This situation is desirable in many situations, especially in medical applications. No current flows between the user's circuit and the BitBox. Information is passed along as light.

Note: the user's GND and the BitBox GND are not connected.

Figure 2-10 The Optocoupler Input

Figure 2-11 Driving the Optocoupler Input with a TTL signal

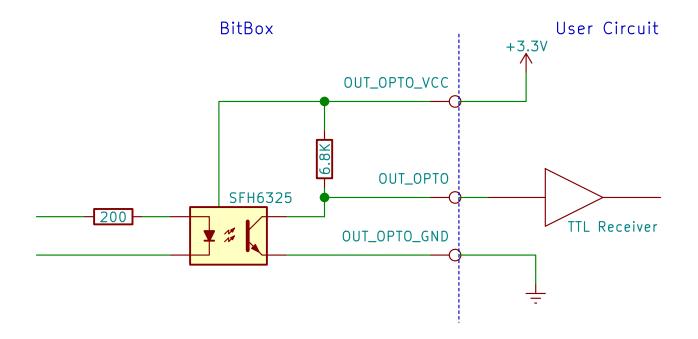

# 2.7 The Optocoupler Outputs

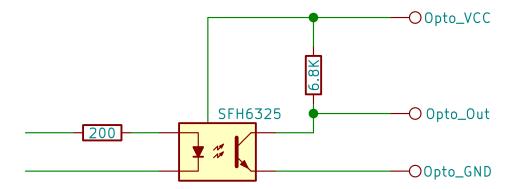

The optocoupler used to output signals off the BitBox is a SFH6325, see Figure 2-12. It has three signals that need to connect to the user's circuit:

- Opto\_Out, the collector of the optocoupler's output transistor.

- Opto\_GND, the emitter of the optocoupler's output transistor.

- Opto\_VCC, power to the optocoupler's output stage; the Opto\_Out is also connected to the Opto\_VCC through a 6.8K pullup resistor.

Figure 2-13 shows a simple connection of the optocoupler output to a user's TTL receiver. The user will supply its own VCC and GND for the optocoupler's output stage. The Opto\_Out will drive the TTL receiver. The key feature of this circuit is that there is no galvanic connection between the BitBox and the user's circuit. The BitBox circuitry will drive the input photodiode which will generate a light inside the optocoupler. This light will induce a current in the output transistor.

Note: the user's GND and the BitBox GND are not connected.

Figure 2-12 The Optocoupler Output

Figure 2-13 Connecting the Optocoupler Output to a TTL Receiver

# 2.8 The 24V Inputs

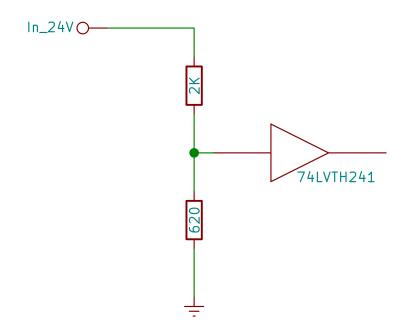

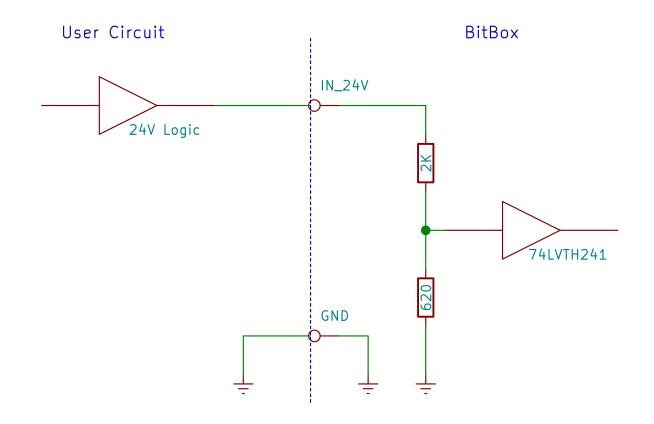

The 24V input to the board has been implemented with a TTL receiver and a voltage divider, see Figure 2-14. Figure 2-15 shows how to connect a 24V logic input source. The user's and the BitBox's GNDs must be connected. Any voltage between 12V and 24V on the In\_24V input will be recognized as a '1' by the TTL receiver. Maximum allowed voltage on In\_24V is 26V.

Figure 2-14 Implementation of the 24V Input

Figure 2-15 Connecting a 24V Input Logic Signal

# 2.9 The Open Collector Outputs

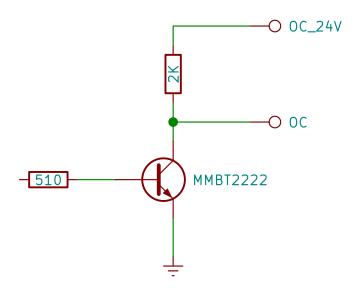

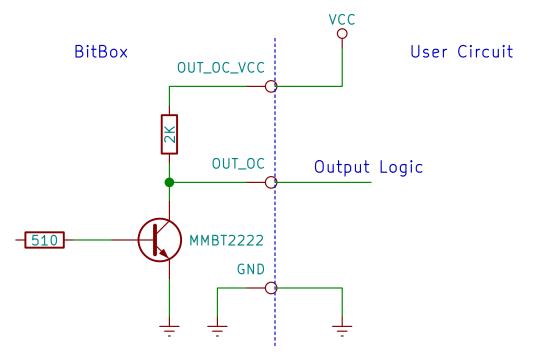

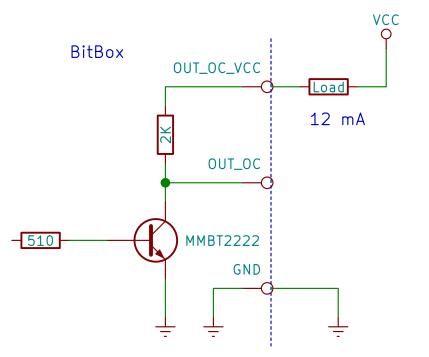

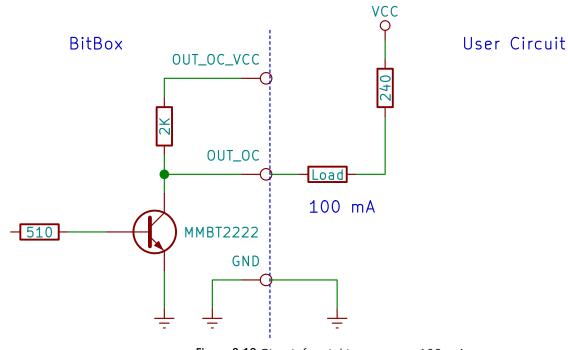

The Open Collector (OC) output has been implemented with a MMBT2222 transistor, see Figure 2-16. The user has access to the collector of the transistor, OC, and to a 2K pullup resistor, OC\_24V. Figure 2-17 shows a simple circuit that supplies a logic output level of up to 24V. The user connects to the OC\_24V output the voltage that he wants the output logic to have in the HI state. For a HI of 24V, connect to a 24V power supply. The maximum voltage is 26V. The minimum voltage is 3V. The user's and the BitBox GNDs must be connected. Figure 2-18 shows a simple circuit that is intended to sink current (as opposed to supplying logic levels). The circuit in Figure 2-18 can sink up to 12 mA. The BitBox's on-board 2K pullup resistor limits the current to 12mA for a 24V power supply. The user's and the BitBox GNDs must be connected. Figure 2-19 shows how to connect a circuit that needs to sink 100mA from 24V. The user's and the BitBox GNDs must be connected. Figure 2-19 shows how to connect a circuit that needs to sink 100mA from 24V. The user's and the BitBox GNDs must be connected.

The maximum current allowed to sink through the transistor is 200mA.

Figure 2-16 Implementation of the Open Collector Output

Figure 2-17 Simple 24 V Output Logic

Figure 2-18 Circuit for sinking current, 12mA

User Circuit

Figure 2-19 Circuit for sinking current, 100 mA

The Open Collector Outputs

# **Timing Sequencer**

# Chapter 3

# 3.1 Introduction

This section covers the Timing Sequencer (TS) which is available on the Cyton-CXP and the Axion-CL. The TS is a sophisticated programmable pulse generator. The TS takes the place of the NTG on previous models of BitFlow frame grabbers.

The TS improves on the NTG in the following ways:

Driven by a "nice" clock frequency clock so that "normal" pulse sizes and periods can easily be reproduce (for example 1 micro second pulse every 10 milliseconds)

Higher accuracy signals, granularity down to 100 nanoseconds

Supports complex pulse trains of different lengths

Provides synchronized method to switch from one pulse sequence to another

Can be reprogrammed while being used (with some restrictions)

Supports triggering at arbitrary points in a pulse train

#### 3.1.1 The Auxiliary Timing Sequencer

The first Virtual Frame Grabber (VFG0) has two independent Timing Sequencers: TS and ATS. They work exactly the same, and have the same control registers. The Auxiliary Timing Sequencer registers are listed here, even though they work in the exact same way as the main timing sequencer. All of the description that follows applies to both the TS and the ATS.

Note: The Auxiliary Timing Sequencer (ATS) is only available on VFG0.

#### 3.1.2 Description

#### TS Table

The TS is programmed through the TS registers. The sequence of pulses that the TS will output is programmed by building up "instructions" in the TS table. The table can hold up to 256 instructions, which can create extremely complex signals. The TS Table is programmed indirectly via address/data type registers. Once the table is programmed it can be run at any time via the TS control registers.

#### **Building Pulses**

The TS was design to support a wide range of pulse lengths. At the same time, the TS was design to be able to create pulses of very accurate duration. The solution to these two opposing problems is to build up a pulse of a desired length via multiple subpulses, each sub-pulse programmed with a different granularity. The following granularities are available:

- 100 seconds

- 100 milliseconds

- 100 microseconds

- 100 nanoseconds

Each sub-pulse can have a length of 1 to 1023 units, where the units are selected from the list above.

For example, let's say you want a pulse that is, for example, 1.2345678 seconds long. This is done by programing the TS table with three sub pulse as shown below:

Entry 1: 12 \* 100 milliseconds = 1.2 seconds Entry 2: 345 \* 100 microseconds = 0.0345 seconds Entry 3: 678 \* 100 nanoseconds = 0.0000678 seconds

When these three entries are "run", they are output sequentially and seamlessly, creating a single pulse of the desired length:

1.2 + 0.0345 + 0.0000678 = 1.2345678

As you can see, this system provides both a wide range of durations as well as very accurate durations.

Pulses can be either high or low (0 or 1). By programming both high pulses and low pulses any pulse train can be created.

#### **Chaining Pulses**

Pulses are chained together by a linked list. Each pulse entry has a "next" field which tells the system where in the table the next pulse should come from. This facility is used to build up complex sequences as well as looping sequences.

#### Triggering

Each entry in the TS table can produce one pulse. Each entry has a "condition" under which it will get executed. The conditions can be immediate. In other words, as soon as the TS gets to this entry, it immediately produces the programmed pules. Or it can be programmed to wait for a trigger. Various trigger conditions are supported.

By adding this condition, the pulse train produced can be run in "one-shot" mode, when one trigger produces one pulse.

# 3.2 TS\_CONTROL

| Bit | Name                 |

|-----|----------------------|

| 0   | TS_RUN_LEVEL         |

| 1   | TS_RUN_LEVEL         |

| 2   | TS_RUN_LEVEL         |

| 3   | Reserved             |

| 4   | TS_CT0_DEFAULT_STATE |

| 5   | TS_CT1_DEFAULT_STATE |

| 6   | TS_CT2_DEFAULT_STATE |

| 7   | TS_CT3_DEFAULT_STATE |

| 8   | Reserved             |

| 9   | Reserved             |

| 10  | Reserved             |

| 11  | Reserved             |

| 12  | Reserved             |

| 13  | Reserved             |

| 14  | Reserved             |

| 15  | Reserved             |

| 16  | TS_IDX_JUMP          |

| 17  | TS_IDX_JUMP          |

| 18  | TS_IDX_JUMP          |

| 19  | TS_IDX_JUMP          |

| 20  | TS_IDX_JUMP          |

| 21  | TS_IDX_JUMP          |

| 22  | TS_IDX_JUMP          |

| 23  | TS_IDX_JUMP          |

| 24  | Reserved             |

| 25  | Reserved             |

| 26  | Reserved             |

| 27  | Reserved             |

| 28  | TS_TRIG_SEL          |

| 29  | TS_TRIG_SEL          |

| 30  | TS_TRIG_SEL          |

| 31  | TS_TRIG_SEL          |

|     |                      |

#### TS\_RUN\_LEVEL R/W, TS\_CONTROL[2..0], Cyton-CXP, Axion-CL, Axion-CL

These bits control the operation of the TS. These bits are used to start and stop the sequencer. They can also be used to program the table to jump to a new section. Jumps are always synchronous (i.e. not immediate). Jumps will only occur from an index in the sequence that has the TS\_END\_OF\_SEQUENCE bit set.

This bit can be read at any time in order get the current status.

The following table shows the command available for this register.

|                          | TS_RUN_LEVEL                   | Meaning                                                                                                                        |

|--------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                          | 0 (000b)                       | Idle - TS is not running                                                                                                       |

|                          | 1 (001b)                       | Run - Start running immediately from index in the TS_IDX_<br>JUMP register                                                     |

|                          | 2 (010b)                       | Jump - Jump to index set in the TS_IDX_JUMP register next<br>time the current index has the TS_END_OF_SEQUENCE bit<br>set to 1 |

|                          | 3 (011b)                       | Stop - Stop running the next time the current index has the TS_END_OF_SEQUENCE bit set to 1                                    |

|                          | 4 (100b)                       | Abort - Stop running immediately                                                                                               |

| TS_CT0_                  | R/W, TS_CONTRO                 | L[4], Cyton-CXP, Axion-CL                                                                                                      |

| DEFAULT_STATE            | This is the output sta         | te of CT0 when the TS is Idle.                                                                                                 |

| TS_CT1_<br>DEFAULT_STATE | R/W, TS_CONTRO                 | L[5], Cyton-CXP, Axion-CL                                                                                                      |

|                          | This is the output sta         | te of CT1 when the TS is Idle.                                                                                                 |

| TS_CT2_                  | R/W, TS_CONTRO                 | L[6], Cyton-CXP, Axion-CL                                                                                                      |

| DEFAULT_STATE            | This is the output sta         | te of CT2 when the TS is Idle.                                                                                                 |

| TS_CT3_                  | R/W, TS_CONTRO                 | L[7], Cyton-CXP, Axion-CL                                                                                                      |

| DEFAULT_STATE            | This is the output sta         | te of CT3 when the TS is Idle.                                                                                                 |

| TS_IDX_JUMP              | R/W, TS_CONTRO                 | L[2316], Cyton-CXP, Axion-CL                                                                                                   |

|                          | This is the entry that<br>Run. | the table will start from when the TS_RUN_LEVEL register is set to                                                             |

to

This is the entry that the table will jump to (synchronously) when the TS\_RUN\_LEVEL register is set to Jump.

### TS\_TRIG\_SEL R/W, TS\_CONTROL[28..31], Cyton-CXP, Axion-CL

These bits select the source of the TS trigger.

| TS_TRIG_SEL | Meaning                                              |

|-------------|------------------------------------------------------|

| 0 (000b)    | Selected trigger (VGFx_TRIG_SEL)                     |

| 1 (001b)    | Selected encoder A (VFGx_ENCA_SEL)                   |

| 2 (010b)    | Selected encoder B (VFGx_ENCB_SEL)                   |

| 3 (011b)    | Selected quad encoder output (VFGx_ENCQ_SEL)         |

| 4 (100b)    | Gated trigger (VGFx_TRIG_SEL gated by VFGx_ENCB_SEL) |

| 5 (101b)    | Selected encoder divider output (VFGx_ENCDIV_SEL)    |

# 3.3 TS\_TABLE\_CONTROL

| Bit | Name          |

|-----|---------------|

| 0   | TS_IDX_ACCESS |

| 1   | TS_IDX_ACCESS |

| 2   | TS_IDX_ACCESS |

| 3   | TS_IDX_ACCESS |

| 4   | TS_IDX_ACCESS |

| 5   | TS_IDX_ACCESS |

| 6   | TS_IDX_ACCESS |

| 7   | TS_IDX_ACCESS |

| 8   | Reserved      |

| 9   | Reserved      |

| 10  | Reserved      |

| 11  | Reserved      |

| 12  | Reserved      |

| 13  | Reserved      |

| 14  | Reserved      |

| 15  | Reserved      |

| 16  | Reserved      |

| 17  | Reserved      |

| 18  | Reserved      |

| 19  | Reserved      |

| 20  | Reserved      |

| 21  | Reserved      |

| 22  | Reserved      |

| 23  | Reserved      |

| 24  | Reserved      |

| 25  | Reserved      |

| 26  | Reserved      |

| 27  | Reserved      |

| 28  | Reserved      |

| 29  | Reserved      |

| 30  | Reserved      |

| 31  | Reserved      |

|     |               |

### TS\_IDX\_ACCESS R/W, TS\_TABLE\_CONTROL[7..0], Cyton-CXP, Axion-CL

Indirect access to the TS table. Set this bitfield to the index value that you wish to modify. Access is done through via TS\_TABLE\_ENTRY register.

# 3.4 TS\_TABLE\_ENTRY

| Bit | Name               |

|-----|--------------------|

| 0   | TS_NEXT            |

| 1   | TS_NEXT            |

| 2   | TS_NEXT            |

| 3   | TS_NEXT            |

| 4   | TS_NEXT            |

| 5   | TS_NEXT            |

| 6   | TS_NEXT            |

| 7   | TS_NEXT            |

| 8   | Reserved           |

| 9   | Reserved           |

| 10  | TS_RESOLUTION      |

| 11  | TS_RESOLUTION      |

| 12  | TS_STATE_CT0       |

| 13  | TS_STATE_CT1       |

| 14  | TS_STATE_CT2       |

| 15  | TS_STATE_CT3       |

| 16  | Reserved           |

| 17  | TS_COUNT           |

| 18  | TS_COUNT           |

| 19  | TS_COUNT           |

| 20  | TS_COUNT           |

| 21  | TS_COUNT           |

| 22  | TS_COUNT           |

| 23  | TS_COUNT           |

| 24  | TS_COUNT           |

| 25  | TS_COUNT           |

| 26  | TS_COUNT           |

| 27  | TS_CONDITION       |

| 28  | TS_CONDITION       |

| 29  | TS_CONDITION       |

| 30  | TS_TERMINATE       |

| 31  | TS_END_OF_SEQUENCE |

|     |                    |

### TS\_NEXT R/W, TS\_TABLE\_ENTRY[7..0], Cyton-CXP, Axion-CL

Index of next pulse. Only relevant if TS\_TERMINATE = 0.

**TS\_RESOLUTION** R/W, TS\_TABLE\_ENTRY[11..10], Cyton-CXP, Axion-CL

The time units of this pulse. The length of this pulse is set in the register TS\_COUNT. The following table shows the available resolutions.

| TS_RESOLUTION | Meaning          |

|---------------|------------------|

| 0 (000b)      | 100 nanoseconds  |

| 1 (001b)      | 100 microseconds |

| 2 (010b)      | 100 milliseconds |

| 3 (011b)      | 100 seconds      |

|               |                  |

**TS\_STATE\_CT0** R/W, TS\_TABLE\_ENTRY[12], Cyton-CXP, Axion-CL

The level of the CT0 signal for this pulse.

**TS\_STATE\_CT1** R/W, TS\_TABLE\_ENTRY[13], Cyton-CXP, Axion-CL

The level of the CT1 signal for this pulse.

**TS\_STATE\_CT2** R/W, TS\_TABLE\_ENTRY[14], Cyton-CXP, Axion-CL

The level of the CT2 signal for this pulse.

**TS\_STATE\_CT3** R/W, TS\_TABLE\_ENTRY[15], Cyton-CXP, Axion-CL

The level of the CT3 signal for this pulse.

**TS\_COUNT** R/W, TS\_TABLE\_ENTRY[26..17], Cyton-CXP, Axion-CL

The length of this pulse. The units for the length are set in the TS\_RESOLUTION register.

### TS\_CONDITION R/W, TS\_TABLE\_ENTRY[29..27], Cyton-CXP, Axion-CL

This register is used to control the conditions under which this pulse will be output. The following table shows the options for this bitfield.

| TS_CONDITION | Condition when pulse is output          |

|--------------|-----------------------------------------|

| 0 (000b)     | Immediate                               |

| 1 (001b)     | Rising edge of trigger                  |

| 2 (010b)     | Falling edge of trigger                 |

| 3 (011b)     | Trigger high                            |

| 4 (100b)     | Trigger low                             |

| 5 (101b)     | Both rising and falling edge of trigger |

#### **TS\_TERMINATE** R/W, TS\_TABLE\_ENTRY[30], Cyton-CXP, Axion-CL

When this bit is set to 0, the table will stop running after the current pulse is output. The TS\_RUN\_LEVEL bitfield will then read back idle.

When this bit is set to 1, the table will jump to the index set in the TS\_NEXT bitfield after the current pulse is finished.

### **TS\_END\_OF\_** R/W, TS\_TABLE\_ENTRY[31], Cyton-CXP, Axion-CL

### SEQUENCE

If this bit is set to 1 and TS\_RUN\_LEVEL is set to Jump, the TS will jump to the index set in the TS\_INDX\_JUMP bitfield after the current pulse is output. This bit allows for synchronous switching between one section of the table and another section.

If the TS\_RUN\_LEVEL bitfield is not set to Jump, then this bitfield will have no effect.

If this bit is set to 0, the TS will not jump from this index.

# 3.5 ATS\_CONTROL

| 0ATS_RUN_LEVEL1ATS_RUN_LEVEL2ATS_RUN_LEVEL3Reserved4ATS_CT0_DEFAULT_STATE5ATS_CT1_DEFAULT_STATE6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP23ATS_IDX_JUMP |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2ATS_RUN_LEVEL3Reserved4ATS_CT0_DEFAULT_STATE5ATS_CT1_DEFAULT_STATE6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                           |

| 3Reserved4ATS_CT0_DEFAULT_STATE5ATS_CT1_DEFAULT_STATE6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                         |

| 4ATS_CT0_DEFAULT_STATE5ATS_CT1_DEFAULT_STATE6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                  |

| 5ATS_CT1_DEFAULT_STATE6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                        |

| 6ATS_CT2_DEFAULT_STATE7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                |

| 7ATS_CT3_DEFAULT_STATE8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                      |

| 8Reserved9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                            |

| 9Reserved10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                     |

| 10Reserved11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                              |

| 11Reserved12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                        |

| 12Reserved13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                  |

| 13Reserved14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                            |

| 14Reserved15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                      |

| 15Reserved16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                |

| 16ATS_IDX_JUMP17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                          |

| 17ATS_IDX_JUMP18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                                        |

| 18ATS_IDX_JUMP19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                                                      |

| 19ATS_IDX_JUMP20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                                                                    |

| 20ATS_IDX_JUMP21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                                                                                  |

| 21ATS_IDX_JUMP22ATS_IDX_JUMP                                                                                                                                                                                                                                                                                                |

| 22 ATS_IDX_JUMP                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                             |

| 23 ATS_IDX_JUMP                                                                                                                                                                                                                                                                                                             |

| 24 Reserved                                                                                                                                                                                                                                                                                                                 |

| 25 Reserved                                                                                                                                                                                                                                                                                                                 |

| 26 Reserved                                                                                                                                                                                                                                                                                                                 |

| 27 Reserved                                                                                                                                                                                                                                                                                                                 |

| 28 ATS_TRIG_SEL                                                                                                                                                                                                                                                                                                             |

| 29 ATS_TRIG_SEL                                                                                                                                                                                                                                                                                                             |

| 30 ATS_TRIG_SEL                                                                                                                                                                                                                                                                                                             |

| 31 ATS_TRIG_SEL                                                                                                                                                                                                                                                                                                             |

### **ATS\_RUN\_LEVEL** R/W, ATS\_CONTROL[2..0], Cyton-CXP, Axion-CL, Axion-CL

These bits control the operation of the ATS. These bits are used to start and stop the sequencer. They can also be used to program the table to jump to a new section. Jumps are always synchronous (i.e. not immediate). Jumps will only occur from an index in the sequence that has the ATS\_END\_OF\_SEQUENCE bit set.

This bit can be read at any time in order get the current status.

The following table shows the command available for this register.

|                           | ATS_RUN_LEVEL                                                                                     | Meaning                                                                                                                          |

|---------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                           | 0 (000b)                                                                                          | Idle - ATS is not running                                                                                                        |

|                           | 1 (001b)                                                                                          | Run - Start running immediately from index in the ATS_IDX_<br>JUMP register                                                      |

|                           | 2 (010b)                                                                                          | Jump - Jump to index set in the ATS_IDX_JUMP register next<br>time the current index has the ATS_END_OF_SEQUENCE bit<br>set to 1 |

|                           | 3 (011b)                                                                                          | Stop - Stop running the next time the current index has the ATS_END_OF_SEQUENCE bit set to 1                                     |

|                           | 4 (100b)                                                                                          | Abort - Stop running immediately                                                                                                 |

| ATS_CT0_<br>DEFAULT_STATE | R/W, ATS_CONTROL[4], Cyton-CXP, Axion-CL<br>This is the output state of CT0 when the ATS is Idle. |                                                                                                                                  |

| ATS_CT1_<br>DEFAULT_STATE |                                                                                                   | OL[5], Cyton-CXP, Axion-CL<br>te of CT1 when the ATS is Idle.                                                                    |

| ATS_CT2_<br>DEFAULT_STATE | R/W, ATS_CONTROL[6], Cyton-CXP, Axion-CL<br>This is the output state of CT2 when the ATS is Idle. |                                                                                                                                  |

| ATS_CT3_<br>DEFAULT_STATE | R/W, ATS_CONTROL[7], Cyton-CXP, Axion-CL<br>This is the output state of CT3 when the ATS is Idle. |                                                                                                                                  |

| ATS_IDX_JUMP              | R/W, ATS_CONTR                                                                                    | OL[2316], Cyton-CXP, Axion-CL                                                                                                    |

|                           | This is the entry that to Run.                                                                    | the table will start from when the ATS_RUN_LEVEL register is set                                                                 |

This is also the entry that the table will jump to (synchronously) when the ATS\_RUN\_ LEVEL register is set to Jump.

### ATS\_TRIG\_SEL R/W, ATS\_CONTROL[28..31], Cyton-CXP, Axion-CL

These bits select the source of the ATS trigger.

| ATS_TRIG_SEL | Meaning                                              |

|--------------|------------------------------------------------------|

| 0 (000b)     | Selected trigger (VGFx_TRIG_SEL)                     |

| 1 (001b)     | Selected encoder A (VFGx_ENCA_SEL)                   |

| 2 (010b)     | Selected encoder B (VFGx_ENCB_SEL)                   |

| 3 (011b)     | Selected quad encoder output (VFGx_ENCQ_SEL)         |

| 4 (100b)     | Gated trigger (VGFx_TRIG_SEL gated by VFGx_ENCB_SEL) |

| 5 (101b)     | Selected encoder divider output (VFGx_ENCDIV_SEL)    |

# 3.6 ATS\_TABLE\_CONTROL

| Bit | Name           |

|-----|----------------|

| 0   | ATS_IDX_ACCESS |

| 1   | ATS_IDX_ACCESS |

| 2   | ATS_IDX_ACCESS |

| 3   | ATS_IDX_ACCESS |

| 4   | ATS_IDX_ACCESS |

| 5   | ATS_IDX_ACCESS |

| 6   | ATS_IDX_ACCESS |

| 7   | ATS_IDX_ACCESS |

| 8   | Reserved       |

| 9   | Reserved       |

| 10  | Reserved       |

| 11  | Reserved       |

| 12  | Reserved       |

| 13  | Reserved       |

| 14  | Reserved       |

| 15  | Reserved       |

| 16  | Reserved       |

| 17  | Reserved       |

| 18  | Reserved       |

| 19  | Reserved       |

| 20  | Reserved       |

| 21  | Reserved       |

| 22  | Reserved       |

| 23  | Reserved       |

| 24  | Reserved       |

| 25  | Reserved       |

| 26  | Reserved       |

| 27  | Reserved       |

| 28  | Reserved       |

| 29  | Reserved       |

| 30  | Reserved       |

| 31  | Reserved       |

|     |                |

R/W, ATS\_TABLE\_CONTROL[7..0], Cyton-CXP, Axion-CL

Indirect access to the TS table. Set this bitfield to the index value that you wish to modify. Access is done through via TS\_TABLE\_ENTRY register.

# 3.7 ATS\_TABLE\_ENTRY

| Bit | Name                |

|-----|---------------------|

| 0   | ATS_NEXT            |

| 1   | ATS_NEXT            |

| 2   | ATS_NEXT            |

| 3   | ATS_NEXT            |

| 4   | ATS_NEXT            |

| 5   | ATS_NEXT            |

| 6   | ATS_NEXT            |

| 7   | ATS_NEXT            |

| 8   | Reserved            |

| 9   | Reserved            |

| 10  | ATS_RESOLUTION      |

| 11  | ATS_RESOLUTION      |

| 12  | ATS_STATE_CT0       |

| 13  | ATS_STATE_CT1       |

| 14  | ATS_STATE_CT2       |

| 15  | ATS_STATE_CT3       |

| 16  | Reserved            |

| 17  | ATS_COUNT           |

| 18  | ATS_COUNT           |

| 19  | ATS_COUNT           |

| 20  | ATS_COUNT           |

| 21  | ATS_COUNT           |

| 22  | ATS_COUNT           |

| 23  | ATS_COUNT           |

| 24  | ATS_COUNT           |

| 25  | ATS_COUNT           |

| 26  | ATS_COUNT           |

| 27  | ATS_CONDITION       |

| 28  | ATS_CONDITION       |

| 29  | ATS_CONDITION       |

| 30  | ATS_TERMINATE       |

| 31  | ATS_END_OF_SEQUENCE |

|     |                     |

RESOLUTION

### ATS\_NEXT R/W, ATS\_TABLE\_ENTRY[7..0], Cyton-CXP, Axion-CL

Index of next pulse. Only follow if ATS\_TERMINATE = 0.

### ATS\_ R/W, ATS\_TABLE\_ENTRY[11..10], Cyton-CXP, Axion-CL

The time units of this pulse. The length of this pulse is set in the register ATS\_COUNT. The following table shows the available resolutions.

| ATS_RESOLUTION | Meaning          |  |

|----------------|------------------|--|

| 0 (000b)       | 100 nanoseconds  |  |

| 1 (001b)       | 100 microseconds |  |

| 2 (010b)       | 100 milliseconds |  |

| 3 (011b)       | 100 seconds      |  |

ATS\_STATE\_CT0 R/W, ATS\_TABLE\_ENTRY[12], Cyton-CXP, Axion-CL

The level of the CT0 signal for this pulse.

ATS\_STATE\_CT1 R/W, ATS\_TABLE\_ENTRY[13], Cyton-CXP, Axion-CL

The level of the CT1 signal for this pulse.

**ATS\_STATE\_CT2** R/W, ATS\_TABLE\_ENTRY[14], Cyton-CXP, Axion-CL

The level of the CT2 signal for this pulse.

**ATS\_STATE\_CT3** R/W, ATS\_TABLE\_ENTRY[15], Cyton-CXP, Axion-CL

The level of the CT3 signal for this pulse.

**ATS\_COUNT** R/W, ATS\_TABLE\_ENTRY[26..17], Cyton-CXP, Axion-CL

The length of this pulse. The units for the length are set in the ATS\_RESOLUTION register.

# ATS\_ R/W, ATS\_TABLE\_ENTRY[29..27], Cyton-CXP, Axion-CL

This register is used to control the conditions under which this pulse will be output. The following table shows the options for this bitfield.

| ATS_CONDITION | Condition when pulse is output          |

|---------------|-----------------------------------------|

| 0 (000b)      | Immediate                               |

| 1 (001b)      | Rising edge of trigger                  |

| 2 (010b)      | Falling edge of trigger                 |

| 3 (011b)      | Trigger high                            |

| 4 (100b)      | Trigger low                             |

| 5 (101b)      | Both rising and falling edge of trigger |

### R/W, ATS\_TABLE\_ENTRY[30], Cyton-CXP, Axion-CL

### TERMINATE

ATS

When this bit is set to 0, the table will stop running after the current pulse is output. The ATS\_RUN\_LEVEL bitfield will then read back idle.

When this bit is set to 1, the table will jump to the index set in the ATS\_NEXT bitfield after the current pulse is finished.

### ATS\_END\_OF\_ R/W, ATS\_TABLE\_ENTRY[31], Cyton-CXP, Axion-CL

### SEQUENCE

If this bit is set to 1 and ATS\_RUN\_LEVEL is set to Jump, the ATS will jump to the index set in the ATS\_INDX\_JUMP bitfield after the current pulse is output. This bit allows for synchronous switching between one section of the table and another section.

If the ATS\_RUN\_LEVEL bitfield is not set to Jump, then this bitfield will have no effect.

If this bit is set to 0, the ATS will not jump from this index.

# The Cyton And Axion I/O System

# Chapter 4

### 4.1 Introduction

The I/O system on the Cyton and Axion family of frame grabbers are based on the Karbon-CXP with some minor changes. This system provides unprecedented flexibility. The goal of this system is to handle all the I/O needs of any machine vision application connected to the real world in a wide variety of ways. The goal is flexibility and observability.

### 4.1.1 Concepts

The basic concept is that the outside world of a machine vision system can have a wide variety of signals, possibly using different electrical standards. The Cyton and/or Axion user can choose whichever ones best suit their needs. These inputs can then be routed to a wide range of internal destinations. Also, the board can generate its own signals of use in this system.

Once the input sources are chosen, they are routed to one of a number of internal signals. These internal signals can then be used to control a wide variety of functions. For example, a function might be to cause the board to acquire a frame.

Finally the internal signals can be routed off the board to a wide number of destinations. These can be used to control something in the outside world. For example, a signal might be routed such that it fires a strobe light or initiates the start of exposure in a camera.

The state of all of the possible inputs can be observed by software at any time by peeking the associated RD\_XXX bit.

### 4.1.2 I/O Between Virtual Frame Grabbers

Because BitFlow's frame grabber can acquire from more than one camera, it has always been a contention between the desire to let each camera be independent, for example, each with its own trigger, and for them to be synchronized, i.e. all cameras using one trigger. The Cyton and Axion I/O system provides for the best of both worlds by fully supporting independent and synchronized triggers using the same flexibility as each individual VFG gets.

What this means is that one of the sources, the master VFG's trigger can be the trigger for all of the VFGs. Thus whatever signal is triggering VFG0, can also trigger all the other VFGs on the board. Of course, each VFG can choose to use the master VFG's trigger, or choose amongst its own sources. Further, the triggers can be synchronized while the encoders are independent.

# 4.2 Overview of the Cyton and Axion I/O System Routing

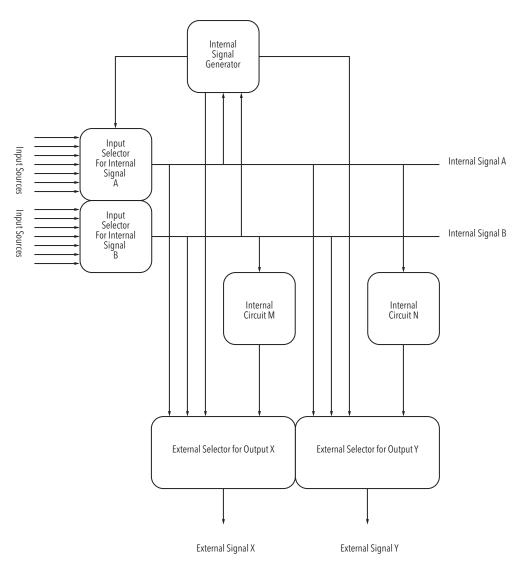

Figure 4-1 below shows a generic version of the I/O system routing. For each internal signal (A and B in this case) a source must be chosen. Each internal signal can be used to control one or more internal circuits or can be routed straight to an output signal. For each output signal (X & Y in this case) a source must be chosen. In addition there are internal signal generators that can be chosen as a source for an internal signal or an external signal. Even the internal signal generators can be triggered by an internal signal.

Note: Figure 4-1 is a schematic version of the actual circuit, it is greatly simplified to make it easier to understand.

Figure 4-1 Conceptual I/O System Routing

### 4.3 Input Selection

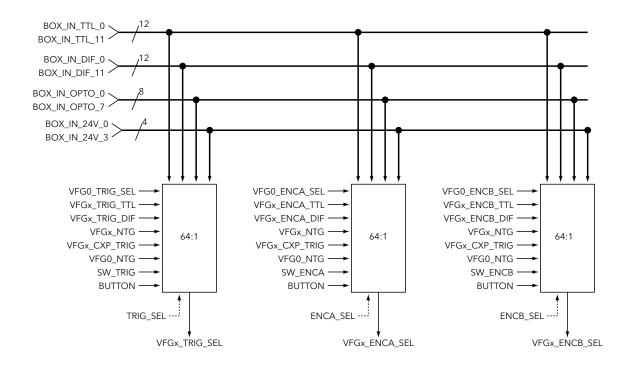

Figure 4-2 illustrates the I/O System input selection circuitry. As discussed above, each internal signal has its own selector. For each internal signal there are 64 possible sources.

Note: The signals BOX\_IN\_XXX are available via an external I/O Box, the BitFlow BitBox, which can be mounted on an external rail system. Contact BitFlow for more information on the BitBox.

Note: Each VFG has a copy of the circuit shown in Figure 4-2. This is why the outputs do not specify the VFG number (e.g. "VFGx\_TRIG\_SEL). However, some inputs do specify the VFG number (e.g. VFG0\_TRIG\_SEL), which means this input comes explicitly from VFG0.

Figure 4-2 I/O System Input Selection

### 4.4 Internal Signals

There are five internal I/O signals. The "x" in the signal name refers to VFG number of the current VFG being used. In general, the "x" is always used as all VFGs are symmetrical. The one exceptions is VFG0, which can route many of its signals to other VFGs on the same physical board. For example VFG2 can use the trigger selected on VFG 0 (i.e. VFG0\_TRIG\_SEL) as its trigger source.

- VFGx\_TRIG\_SEL normally used as a frame trigger, can also be used to initiate acquisition of N frames, or can be use to control the start and end of a frame when used with a line scan camera.

- VFGx\_ENCA\_SEL Normally used as a line trigger, to initiate the capture of one line. When using a single phase encoder, this is the signal to use.

- VFGx\_ENCB\_SEL Normally used as a line trigger when using a quadrature encoder. The encoder B should be the second phase of the quadrature encoder with Encoder A being the first phase.

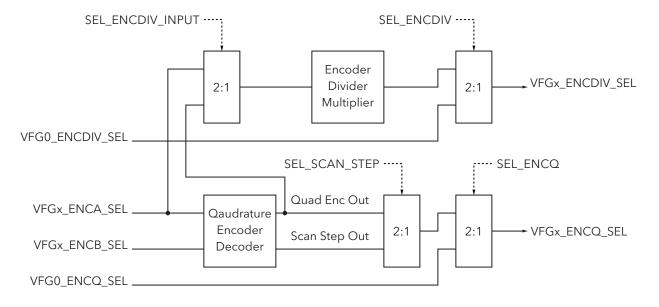

- VFGx\_ENCDIV\_SEL This signal is the output of the encoder divider (multiplier) circuit. This circuit can be driven by more than one source. The output signal is related to the input signal, but the frequency is either divided down or multiplied up.

- VFGx\_ENCQ\_SEL This signal is the output of the quadrature encoder circuit. This circuit takes to inputs, the selected encoder A and the selected encoder B. The output signal follows the rules as programmed in to the quadrature encoder circuit, see Section 8.1 for more information.

Note: The internal signals have names such as "Trigger" and "Encoder" because they are hardwired to certain internal circuits. However, if you are not using them for this functionality, they can be used for any purpose that the routing supports.

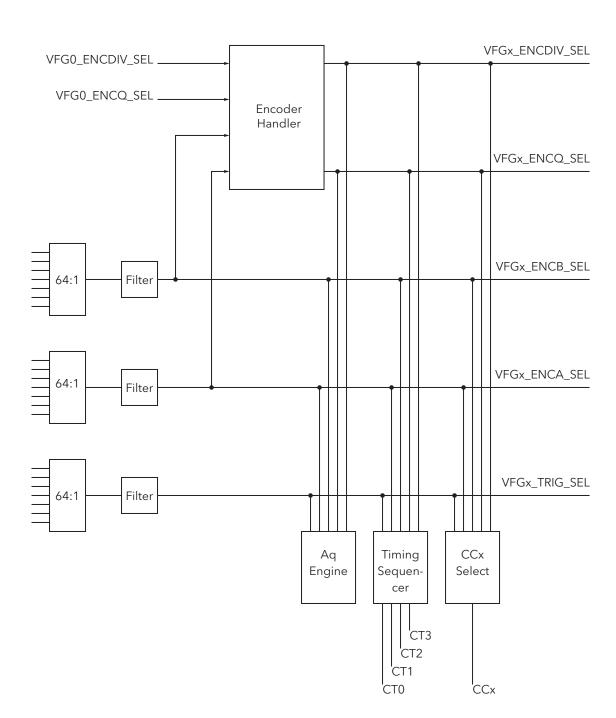

Each of the internal signals is hardwired to a number of destinations. Even though a signal might be connected to a circuit, the circuit may not be "listening" to the signal. Each circuit has its own control registers which tells it to use a given signal or not. Figure 4-3 shows all the internal circuits that each internal signal is connected to.

Figure 4-4 shows the details of the encoder handler block that is part of Figure 4-3.

The Filter is used to remove unwanted noise on the incoming signal. The filter is programmable and it will "swallow" a pulse shorter than the programmed size. The Cyton And Axion I/O System

Figure 4-3 Internal Signal Routing

Figure 4-4 Encoder Handler

## 4.5 Output Signal Selection

There are four dynamic output signals for each VFG, CC1 to CC4, and thirty six static output signals, VFG0\_GPOUTx\_Xxx, which are only on VFG0. The dynamic signals can be driven by a variety of sources as shown in Figure 4-5. The static signals are controlled by the values in the registers with the same names (e.g. VFG0\_GPOUT0\_TTL is controlled by the register BOX\_OUT\_GPOUT0\_TTL) in VFG0.

Figure 4-5 Output Signal Source Selection

# 4.6 I/O Connector Output Signal Routing

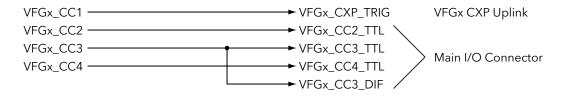

The CCx output signals are routed to the CXP link or the board's main I/O connector Figure 4-6 illustrates how they are routed.

Note: Each VFG has an instance of the circuit shown below. This means each VFG has its own CC2, CC3 and CC4 signals present on the board's main I/O connector.

Note: The signals VFGx\_CC1 to VFGx\_CC3 can be sourced from many different signals. Please see Section 4.5 for more information on selecting the source.

Note: The signals VFGx\_CC1 to VFGx\_CC3 can also be routed to the BitBox, which is an externally mountable I/O Box.

Figure 4-6 Output Signal Routing

# 4.7 BitBox Output Signal Routing

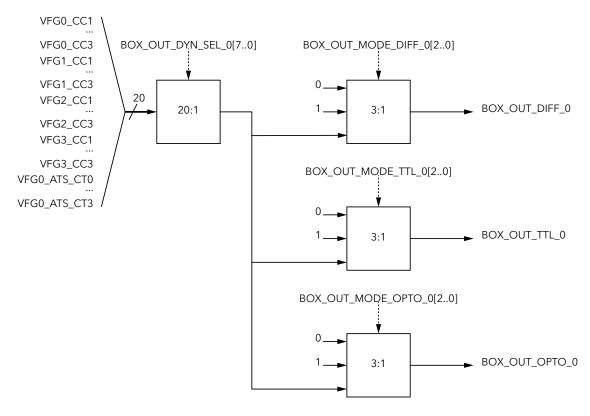

The BitFlow BitBox has 3 banks of 12 outputs. One bank is TTL, one bank is differential and one bank is a mix of Optocoupled and Open Collector outputs. Each of the 36 outputs can be set to a static output level, or controlled by a dynamic source (waveform). Figure 4-7 shows how the outputs are controlled.

Note: Figure 4-7 shows the choices and routing for just 3 outputs. A total of 12 of these circuits (each with their own control registers) are required on the board in order to control 36 outputs.

Figure 4-7 BitBox Output Signal Routing

Note: The BitFlow BitBox is an externally rail mounted box which can take a wide variaty of inputs and outputs. It is connected to the Cyton/Axion though a small cable. Contact BitFlow for more information on the BitBox.

# The Cyton and Axion I/O System Registers

# Chapter 5

## 5.1 Introduction

The registers documented in this section are used to control the I/O system on the Cyton-CXP and the Axion-CL

## 5.2 CON60

| Bit | Name             |

|-----|------------------|

| 0   | RD_BOX_IN_TTL_0  |

| 1   | RD_BOX_IN_TTL_1  |

| 2   | RD_BOX_IN_TTL_2  |

| 3   | RD_BOX_IN_TTL_3  |

| 4   | RD_BOX_IN_TTL_4  |

| 5   | RD_BOX_IN_TTL_5  |

| 6   | RD_BOX_IN_TTL_6  |

| 7   | RD_BOX_IN_TTL_7  |

| 8   | RD_BOX_IN_TTL_8  |

| 9   | RD_BOX_IN_TTL_9  |

| 10  | RD_BOX_IN_TTL_10 |

| 11  | RD_BOX_IN_TTL_11 |

| 12  | RD_BOX_IN_DIF_0  |

| 13  | RD_BOX_IN_DIF_1  |

| 14  | RD_BOX_IN_DIF_2  |

| 15  | RD_BOX_IN_DIF_3  |

| 16  | RD_BOX_IN_DIF_4  |

| 17  | RD_BOX_IN_DIF_5  |

| 18  | RD_BOX_IN_DIF_6  |

| 19  | RD_BOX_IN_DIF_7  |

| 20  | RD_BOX_IN_DIF_8  |

| 21  | RD_BOX_IN_DIF_9  |

| 22  | RD_BOX_IN_DIF_10 |

| 23  | RD_BOX_IN_DIF_11 |

| 24  | ENINT_CXP        |

| 25  | INT_CXP          |

| 26  | Reserved         |

| 27  | Reserved         |

| 28  | Reserved         |

| 29  | SW_TRIG          |

| 30  | SW_ENCA          |

| 31  | SW_ENCB          |

| RD_BOX_IN_          | RO, CON60[110], Cyton-CXP, Axion-CL                                                                                                                                    |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| πι_χ                | These bits reflect the real-time state of the 12 TTL inputs on the BitBox.                                                                                             |

| RD_BOX_IN_<br>DIF_X | RO, CON60[2312], Cyton-CXP, Axion-CL                                                                                                                                   |

| -                   | These bits reflect the real-time state of the 12 differential inputs on the BitBox.                                                                                    |

| ENINT_CXP           | R/W, CON60[24], Cyton-CXP, Axion-CL                                                                                                                                    |

|                     | This bit enables interrupts from the CXP subsystem.                                                                                                                    |

| INT_CXP             | RO, CON60[25], Cyton-CXP, Axion-CL                                                                                                                                     |

|                     | This bit indicates the existence of an interrupt from the CXP subsystem. The individual interrupt must be cleared in the CXP subsystem in order for this bit to reset. |

| SW_TRIG             | R/W, CON60[29], Cyton-CXP, Axion-CL                                                                                                                                    |

|                     | Writing the bit to 1 causes the internal software trigger signal to be asserted. Writing it to a 0 will de-assert the internal software trigger signal.                |

| SW_ENCA             | R/W, CON60[30], Cyton-CXP, Axion-CL                                                                                                                                    |

|                     | Writing the bit to 1 causes the internal encoder A signal to be asserted. Writing it to a 0 will de-assert the internal encoder A signal.                              |

| SW_ENCB             | R/W, CON60[31], Cyton-CXP, Axion-CL                                                                                                                                    |

|                     | Writing the bit to 1 causes the internal encoder B signal to be asserted. Writing it to a 0 will de-assert the internal encoder B signal.                              |

# 5.3 CON61

| Bit | Name             |

|-----|------------------|

| 0   | RD_BOX_IN_OPTO_0 |

| 1   | RD_BOX_IN_OPTO_1 |

| 2   | RD_BOX_IN_OPTO_2 |

| 3   | RD_BOX_IN_OPTO_3 |

| 4   | RD_BOX_IN_OPTO_4 |

| 5   | RD_BOX_IN_OPTO_5 |

| 6   | RD_BOX_IN_OPTO_6 |

| 7   | RD_BOX_IN_OPTO_7 |

| 8   | RD_BOX_IN_24V_0  |

| 9   | RD_BOX_IN_24V_1  |

| 10  | RD_BOX_IN_24V_2  |

| 11  | RD_BOX_IN_24V_3  |

| 12  | Reserved         |

| 13  | Reserved         |

| 14  | Reserved         |

| 15  | Reserved         |

| 16  | Reserved         |

| 17  | Reserved         |

| 18  | Reserved         |

| 19  | Reserved         |

| 20  | Reserved         |

| 21  | Reserved         |

| 22  | Reserved         |

| 23  | RD_CXP_TRIG_OUT  |

| 24  | Reserved         |

| 25  | Reserved         |

| 26  | Reserved         |

| 27  | Reserved         |

| 28  | Reserved         |

| 29  | Reserved         |

| 30  | Reserved         |

| 31  | Reserved         |

# **RD\_BOX\_IN\_** RO, CON61[7..0], Cyton-CXP, Axion-CL **OPTO\_X**

These bits reflect the real-time state of the eight Opto-Isolated inputs on the BitBox.

| RD_BOX_IN_ | RO, CON61[118], Cyton-CXP, Axion-CL                                          |

|------------|------------------------------------------------------------------------------|

| 24V_X      |                                                                              |

|            | These bits reflect the real-time state of the four 24V inputs on the BitBox. |

|            |                                                                              |

**RD\_CXP\_TRIG\_** RO, CON61[23], Cyton-CXP, Axion-CL **OUT**

This bit reflects the real-time state of the CXP trigger signal going to the camera.

## 5.4 CON62

| Bit | Name             |

|-----|------------------|

| 0   | RD_TRIG_TTL      |

| 1   | RD_TRIG_DIF      |

| 2   | RD_TRIG_VFG0     |

| 3   | RD_SCAN_STEP     |

| 4   | RD_SW_TRIG       |

| 5   | RD_ENCA_TTL      |

| 6   | RD_ENCA_DIF      |

| 7   | RD_ENCA_VFG0     |

| 8   | RD_ENCA_SW       |

| 9   | RD_ENCB_TTL      |

| 10  | RD_ENCB_DIF      |

| 11  | RD_ENCB_VFG0     |

| 12  | RD_ENCB_SW       |

| 13  | RD_BUTTON        |

| 14  | Reserved         |

| 15  | Reserved         |

| 16  | Reserved         |

| 17  | Reserved         |

| 18  | Reserved         |

| 19  | Reserved         |

| 20  | Reserved         |

| 21  | Reserved         |

| 22  | Reserved         |

| 23  | Reserved         |

| 24  | RD_CXP_TRIG_IN   |

| 25  | EN_TRIG          |

| 26  | EN_ENCA          |

| 27  | EN_ENCB          |

| 28  | Reserved         |

| 29  | RD_ENCB_SELECTED |

| 30  | RD_ENCA_SELECTED |

| 31  | RD_TRIG_SELECTED |

|     |                  |

### **RD\_TRIG\_TTL** RO, CON62[0], Cyton-CXP, Axion-CL

This bit reflects the real-time state of the VFG's TTL trigger input.

**RD\_TRIG\_DIF** RO, CON62[1], Cyton-CXP, Axion-CL

This bit reflects the real-time state of the VFG's differential trigger input.

**RD\_TRIG\_VFG0** RO, CON62[2], Cyton-CXP, Axion-CL

This bit reflects the real-time state of VFG0's selected trigger signal.

**RD\_SCAN\_STEP** RO, CON62[3], Cyton-CXP, Axion-CL

This bit reflects the real-time state of the VFG's scan step circuitry output (from the quadrature encoder circuit).